# Module Placement with Boundary Constraints Using B\*-trees

Jai-Ming Lin<sup>1</sup>, Huai-En  $Y_i^1$ , and Yao-Wen Chang<sup>2</sup>

#### Abstract

The module placement problem is to determine the coordinates of logic modules in a chip such that no two modules overlap and some cost (e.g., silicon area, interconnection length, etc) is optimized. To shorten connections between inputs and outputs and/or make related modules adjacent, it is desired to place some modules along the specific boundaries of a chip. To deal with such boundary constraints, we explore the feasibility conditions of a B\*-tree with boundary constraints and develop a simulated annealing based algorithm using B\*-trees. Unlike most previous works, our algorithm guarantees a feasible B\*-tree with boundary constraints for each perturbation. Experimental results show that our algorithm can obtain smaller silicon area than the most recent work based on sequence pair.

## 1 Introduction

As circuit complexity increases dramatically, hierarchical design and IP modules are widely used in modern VLSI design. This trend makes floorplanning/placement much more critical than ever. Floorplanning/placement is to determine shapes and positions of modules to optimize circuit performance. Since geometric relations among modules are determined during floorplanning/placement, the results have a great impact on the quality and flexibility of a design, such as layout area, global routing structure, and power consumption, etc. To facilitate floorplan design, we need a representation that can record the geometric relationship among modules, can be manipulated efficiently, and can handle various constraints. Among the floorplanning/placement constraints, boundary constraints, which require some modules to be placed along the chip boundaries, are often concerned in the real design. There are at least two situations that motivate the consideration of boundary constraints:

• In order to shorten connections between inputs and outputs, it is desired to place some modules along the specific boundaries of a chip.

<sup>\*</sup>This work was partially supported by the National Science Council of Taiwan ROC under Grant No. NSC-89-2215-E-009-117.

†Jai-Ming Lin and Huai-En Yi are with the Department of Computer and Information Science, National Chiao Tung Univer-

sity, Hsinchu 300, Taiwan. E-mail: {gis87808, gis88519}@cis.nctu.edu.tw. Yao-Wen Chang is with the Department of Electrical Engineering & Graduate Institute of Electronics Engineering, National Taiwan University, Taipei 106, Taiwan. E-mail: ywchang@cc.ee.ntu.edu.tw.

To deal with large circuits hierarchically, modules are grouped into units and module placement is

performed independently for each unit. It will be helpful if some modules are constrained to be

placed along boundaries in each unit such that they can be adjacent to some other modules in the

neighboring units.

Therefore, it is desired to develop an efficient and effective approach to the floorplanning/placement problem with boundary constraints.

#### 1.1 Previous Work

Floorplans are often handled based on their structures, the slicing structure [10], [15] and the non-slicing one [1], [2], [3], [6], [8], and [9]. A slicing structure can be obtained by recursively cutting rectangles horizontally or vertically into smaller rectangles; otherwise, it is a non-slicing structure. For the slicing structure, Otten in [10] first used a binary tree to represent the slicing floorplan. Wong and Liu later in [15] proposed a normalized Polish expression to improve the binary tree-based representation. The slicing structure has smaller solution space, resulting in faster running time. However, the non-slicing structure is more general and often leads to a more area-efficient placement than the slicing one.

There are a few new non-slicing floorplan representations in the literature, e.g., sequence pair (SP) [8], bounded-slicing grid (BSG) [9], O-tree [2], B\*-tree [1], corner block list (CBL) [3], and transitive closure graph (TCG) [6]. Murata et al. in [8] used two sequences of module names, called SP, to represent the geometric relations among modules. Another representation, called BSG, was later proposed by Nakatake et al. [9]. Guo et al. in [2] first proposed a tree-based representation, O-tree, for non-slicing floorplans. Chang et al. in [1] presented a binary tree-based representation, called B\*-tree, and showed its superior properties for operations. Hong et al. in [3] proposed the CBL representation for non-slicing floorplans. Recently, Lin and Chang in [6] proposed a new representation, called TCG, by using a pair of transitive closure graphs.

The floorplan design with boundary constraints was first studied by Young and Wong [16]. They applied the normalized Polished expression to handle the problem with a slicing floorplan. Recently, several approaches for the problem for non-slicing floorplans are presented. Tang and Wong in [13] handled the constraint by adding dummy edges into the constraint graphs of SP; however, they just presented their idea without implementing their approach. Based on CBL, Ma et al. in [7] assigned a penalty to a misplaced boundary module and perturbed CBL to reduce the penalty. All the previous works in [7], [13], and [16] cannot guarantee a feasible solution after solution perturbation and their final placements. Unlike the previous works, Lai et al. in [5] explored the feasibility conditions for SP with boundary constraints and transformed an infeasible solution into a feasible one to guarantee a feasible solution in each perturbation. However, the method is very complex, and many rules are needed to cope with the constraints.

### 1.2 Our Contribution

In this paper, we deal with the floorplan design with boundary constraints using the B\*-tree representation because it has been proved a superior representation due to its simple, yet effective binary tree structure. We first explore the feasibility conditions of a B\*-tree with boundary constraints and develop a simulated annealing based algorithm using B\*-trees. Unlike the previous works proposed by Yong and Wong [16], Tang and Wong [13], and Ma et al. [7], our algorithm guarantees a feasible B\*-tree with boundary constraints for each perturbation. Unlike the complicated rules using SP proposed by Lai et al. [5] to guarantee a feasible solution for each perturbation, our method is very simple and easy for implementation. Experimental results show that our algorithm can obtain smaller silicon area than the most recent work by Lai et al. [5].

The remainder of this paper is organized as follows. Section 2 formulates the floorplanning/placement design problem with boundary constraints. Section 3 reviews the B\*-tree representation. Section 4 explores the feasibility conditions of a B\*-tree with boundary constraints. Section 5 presented our algorithm. Experimental results are reported in Section 6. Finally, we conclude our work in Section 7.

### 2 Problem Formulation

Given a set of modules  $M = \{m_1, m_2, ..., m_n\}$ , where each module  $m_i$ ,  $1 \le i \le n$ , has a fixed area, and its width, height, and area are denoted by  $w_i$ ,  $h_i$ , and  $A_i$ , respectively. Each module  $m_i$  is free to rotate. Let F denote those modules without any boundary constraints (i.e., modules in F are free to be placed anywhere in the final placement). On the other hand, let T(L, B, or R) denote a set of modules that are demanded to be placed along the top (left, bottom, or right) boundary in the final placement. Therefore, we can divide M into five disjoint subsets F, T, B, L and R (i.e.,  $M = F \cup T \cup B \cup L \cup R$ ). T, B, L, or R may be an empty set if there exists no module with such a boundary constraint in placement.

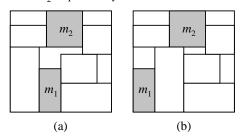

Figure 1 gives an example of a placement with boundary-constrained modules. Module  $m_1(m_2)$  denotes a left (top) boundary module. Figure 1(a) shows an infeasible placement since  $m_1$  is not placed along the left boundary while Figure 1(b) gives a feasible placement since  $m_1$  and  $m_2$  are placed at the designated boundaries.

Let  $(x_i, y_i)$  denote coordinate of the bottom-left corner of  $m_i$ ,  $1 \le i \le n$ , on a chip. A placement P with boundary-constrained modules is an assignment of  $(x_i, y_i)$  for each  $m_i$  such that no two modules overlap and the modules in  $T \cup B \cup L \cup R$  satisfy designated boundary constraints. The goal of a placement with boundary constraints is to minimize the total area (i.e., the minimum bounding rectangle of P). We do not consider the optimization of interconnect wirelength in this paper. However, it can be done easily by adding it into the cost function of our algorithm.

$m_1$ : left boundary–constrained module  $m_2$ : top boundary–constrained module

Figure 1: A placement with boundary-constrained modules (module  $m_1$  ( $m_2$ ) denotes a left (top) boundary module). (a) An infeasible placement because there exists a module at the left-hand side of  $m_1$ . (b) A feasible placement.

# 3 B\*-tree Representation

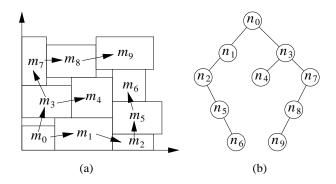

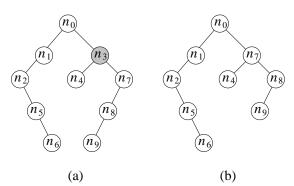

Before introducing our method, we shall first review the  $B^*$ -tree representation. Chang et al. in [1] presented a binary tree-based representation for a left and bottom compacted placement, called  $B^*$ -tree, and showed its superior properties for operations. Given a placement P, we can construct a unique (horizontal)  $B^*$ -tree in linear time by using a recursive procedure similar to the depth first search (DFS) algorithm. (See Figure 2(b) for the corresponding  $B^*$ -tree of the placement shown in Figure 2(a).) Each node  $n_i$  in a  $B^*$ -tree denotes a module. The root of a  $B^*$ -tree corresponds to the module on the bottom-left corner. The left child  $n_j$  of a node  $n_i$  denotes the module  $m_j$  that is the lowest adjacent module on the right-hand side of  $m_i$  (i.e.,  $x_j = x_i + w_i$ ). The right child  $n_k$  of a node  $n_i$  denotes module  $m_k$  that is the lowest visible module above  $m_i$  and with the same x coordinate as  $m_i$  (i.e.,  $x_k = x_i$ ).

Figure 2: (a) A placement. (b) The corresponding B\*-tree.

Figures 2(a) and (b) show a placement and its corresponding B\*-tree, respectively. The root  $n_0$  of the B\*-tree in Figures 2(b) denotes that  $m_0$  is the module on the bottom-left corner of the placement. For node  $n_3$  in the B\*-tree,  $n_3$  has a left child  $n_4$ , which means that module  $m_4$  is the lowest adjacent module in the right-hand side of module  $m_3$  (i.e.,  $x_4 = x_3 + w_3$ ).  $n_7$  is the right child of  $n_3$  since module  $m_7$  is the visible module over module  $m_3$  and the two modules have the same x coordinate ( $x_7 = x_3$ ).

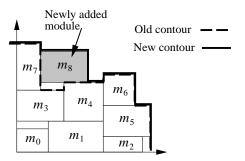

We shall show the procedure to get the placement from a B\*-tree. We first introduce a *contour* structure, which is used by Guo et al. in [2]. The contour structure is a doubly linked list of modules, which describes the contour line in the current compaction direction. Without the contour structure, the runtime for placing a new module is linear to the number of modules. By maintaining the contour structure, the y-coordinate for a newly inserted module can be computed in O(1) time. Figure 3 illustrates how to update the contour when we add a new module  $m_8$  to the placement. The old contour is composed of modules  $m_7$ ,  $m_3$ ,  $m_4$ ,  $m_6$ , and  $m_5$ . After  $m_8$  is placed, the new contour becomes  $m_7$ ,  $m_8$ ,  $m_4$ ,  $m_6$ , and  $m_5$ . Note that we only need to search modules  $m_3$  and  $m_4$  to get its y coordinate  $y_8$  with the contour structure.

Figure 3: Adding a new module on top, we search the contour from left to right and update it with the top boundary of the new module.

## 4 B\*-tree for Boundary-Constrained Modules

In this section, we first explore the properties of a B\*-tree with boundary constraints. We then present the feasibility conditions of a B\*-tree with the constraint.

#### 4.1 Properties of B\*-tree

The boundary-constrained modules are those modules that must be placed along boundaries in the final placement. A module can be placed along the bottom (left) boundary if there exists no module below (left to) the module in the final placement. Similarly, a module can be placed along the top (right) boundary if there exists no module above (right to) the module in the final placement. By the definition of a B\*-tree, the left child  $n_j$  of a node  $n_i$  represents the lowest adjacent module  $b_j$  to the right of  $b_i$  (i.e.,  $x_j = x_i + w_i$ ). The right child  $n_k$  of  $n_i$  represents the lowest visible module  $b_k$  above  $b_i$  and with the same x coordinate as  $b_i$  (i.e.,  $x_k = x_i$ ). Therefore, we have the following four properties in order to guarantee that there exists no module below, left to, right to, and above the module along the bottom, left, right, and top boundaries, respectively.

**Property 1** In a  $B^*$ -tree, we have the properties for boundary constraints.

- 1. The node corresponding to a bottom boundary module cannot be the right child of others.

- 2. The node corresponding to a left boundary module cannot be the left child of others.

- 3. The node corresponding to a right boundary module cannot have a left child.

- 4. The node corresponding to a top boundary module cannot have a right child.

## 4.2 Feasibility Conditions of B\*-tree

The properties mentioned in the preceding subsection must be satisfied in order to guarantee a feasible B\*-tree with boundary-constrained modules. However, they only describe the necessary conditions for a B\*-tree with the boundary constraints, that is, a module may not be placed along the designated boundary if the corresponding property is satisfied. See Figure 2 for an example. Although node  $n_4$  in Figure 2(b) does not have a left (right) child, module  $m_4$  is not placed at the right (top) boundary in Figure 2(a). In order to guarantee that modules are placed at designated boundaries, we propose sufficient conditions for a B\*-tree with boundary constraints.

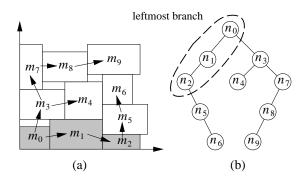

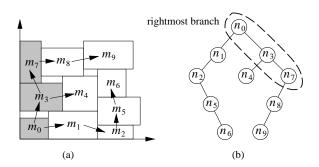

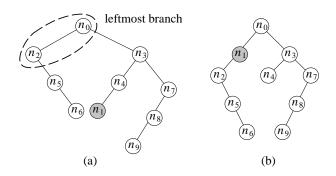

Let the *leftmost branch* (*rightmost branch*) of a B\*-tree denote the path formed by the root and its leftmost (rightmost) descendants. See Figure 4(b) (Figure 5(b)) for the leftmost (rightmost) branch in a B\*-tree. All nodes in the leftmost (rightmost) branch are not right (left) children of others; therefore, the nodes in the leftmost (rightmost) branch satisfy Property 1 (Property 2), which means that there exists no module below (left to) the corresponding module. By the definition of B\*-tree, module  $m_j$  should be adjacent and right to  $m_i$  if  $n_j$  is left child of the node  $n_i$ . The modules corresponding to the nodes in the leftmost branch should be placed at the bottom-left corner or right to the module placed at the bottom-left corner. Therefore, these modules must be placed along the bottom boundary. Similarly,  $m_k$  is the lowest visible module above  $m_i$  and with the same x coordinate with  $m_i$  if  $n_k$  is the right child of  $n_i$ . The modules corresponding to the nodes in the rightmost branch should be placed at the bottom-left corner or above and with the same x coordinate with the module placed at the bottom-left corner. Therefore, these modules must be placed along the left boundary. We thus have the following theorem for the feasibility conditions of a B\*-tree with the bottom and the left constraints.

### **Theorem 1** (Feasibility Conditions)

- Bottom-boundary condition: The nodes corresponding to the bottom boundary modules must be in the leftmost branch of a B\*-tree.

- Left-boundary condition: The nodes corresponding to the left boundary modules must be in the rightmost branch of a B\*-tree.

Figures 4(a) and (b) show a placement and its corresponding B\*-tree. Modules  $m_0$ ,  $m_1$ , and  $m_2$  in Figure 4(a) are bottom boundary modules and the corresponding nodes  $n_0$ ,  $n_1$ , and  $n_2$  are in the leftmost branch of a B\*-tree of Figure 4(b). Similarly, Figures 5(a) and (b) show a placement with left boundary modules  $m_0$ ,  $m_3$ , and  $m_7$  and the corresponding B\*-tree with nodes  $n_0$ ,  $n_3$ , and  $n_7$  in the rightmost branch.

Figure 4: (a) The bottom boundary modules. (b) The corresponding nodes in the leftmost branch.

Figure 5: (a) The left boundary modules. (b) The corresponding nodes in the rightmost branch.

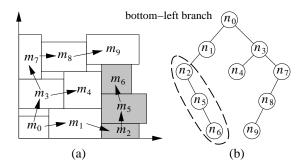

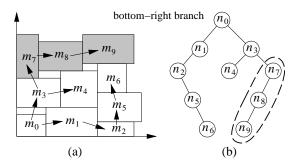

Let the *bottom-left branch* (*bottom-right branch*) of a B\*-tree denote the path formed by the end of the leftmost (rightmost) branch and its rightmost (leftmost) descendants. See Figure 6(b) (Figure 7(b)) for the bottom-left (bottom-right) branch of a B\*-tree. However, there may exist left (right) children for the nodes in the bottom-left (bottom-right) branch; therefore, the nodes in the branch may not satisfy *Property 3* (*Property 4*). In order to guarantee that modules can be placed along the right (top) boundary, their left (right) children are deleted. By the definition of B\*-tree, the modules corresponding to the nodes in the bottom-left branch are placed at the bottom-right corner or above and with the same x coordinate with the module placed at the bottom-right corner. Further, no module is placed right to these modules since the left children for the nodes in the bottom-left branch are deleted. Similarly, the modules corresponding to the nodes in the bottom-right branch are placed at the top-left corner or right to the module at the top-left corner. Further, no module is placed above these modules since the right children of the nodes in the bottom-right branch are deleted. We thus have the following theorem for the feasibility conditions of a B\*-tree with the right and the top boundary constraints.

### **Theorem 2** (Feasibility Conditions)

• Right-boundary condition: For the right boundary modules, their corresponding nodes are in the bottom-left branch of a B\*-tree with the left child for each node in the path being deleted.

• Top-boundary condition: For the top boundary modules, their corresponding nodes are in the bottomright branch of a B\*-tree with the right child for each node in the path being deleted.

Figure 6: (a) The right boundary modules. (b) The corresponding nodes in the bottom-left branch.

Figure 7: (a) The top boundary modules. (b) The corresponding nodes in the bottom-right branch.

Figures 6(a) and (b) show a placement and the corresponding B\*-tree. Modules  $m_2$ ,  $m_5$ , and  $m_6$  in Figure 6(a) denote the right boundary modules and the corresponding nodes  $n_2$ ,  $n_5$ , and  $n_6$  are in the bottom-left branch of the B\*-tree in Figure 6(a). Besides,  $n_2$ ,  $n_5$ , and  $n_6$  have no left child. Similarly, Figures 7(a) and (b) show a placement with top boundary modules  $m_7$ ,  $m_8$ , and  $m_9$  and the corresponding B\*-tree with nodes  $n_7$ ,  $n_8$ , and  $n_9$  in the bottom-right branch. It should be noted that  $m_9$  is also a module along the right boundary, which cannot be identified by the right-boundary condition. To identify it, we shall find the last node in the bottom-left branch, which corresponds to the module at the top right corner.

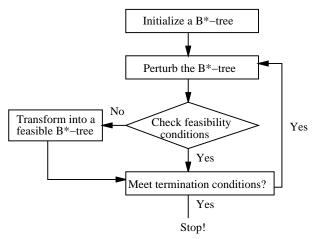

## 5 The Placement Algorithm

Based on B\*-trees, we develop a simulated annealing based algorithm [4] for handling the placement with boundary constraints. Given an initial B\*-tree, the algorithm perturbs the B\*-tree to get a new one. Then, the four feasibility conditions of B\*-trees are checked. We transform an infeasible B\*-tree into feasible one if any condition is violated. The perturbation process repeats until pre-defined termination conditions are met. See Figure 8 for the flow of our algorithm.

Figure 8: The flow of our algorithm.

### 5.1 Solution Perturbation

We apply the following three operations to perturb a B\*-tree:

• Op1: Rotate a module.

• Op2: Swap two modules.

• Op3: Move a module to another place.

Op1 only exchanges the width and height of a module without changing a  $B^*$ -tree while Op2 and Op3 do. Only two nodes in a  $B^*$ -tree are exchanged for Op2. The time complexity of Op2 takes O(1) time. However, the topology of a  $B^*$ -tree is changed for Op3 since we need to delete and insert nodes into the  $B^*$ -tree. The operations for deleting and inserting nodes are described in the following.

For node deletion, three types of nodes must be considered: leaf nodes, nodes with one child, and nodes with two children. For a leaf node, it can be removed from a B\*-tree directly without affecting other nodes. For a node with one child, it is replaced by its child. The subtree rooted by the child remains unchanged after the deletion. This tree update can be performed in O(1) time. The process to delete a node with two children is a bit more complex. One of its two children is chosen to replace the target node. Then we move a child of the node to the position of the node. The procedure continues until the corresponding leaf node is processed. This operation takes O(h) time, where h is the height of B\*-tree. See Figure 9 for an example. The node  $n_3$  in Figure 9(a) is to be deleted from the B\*-tree. Since  $n_3$  has two children  $n_4$  and  $n_7$ , we randomly choose a node  $n_7$  to replace  $n_3$ , and then use the child  $n_8$  of  $n_7$  to replace  $n_7$ , and so on. The resulting B\*-tree is shown in Figure 9(b).

When we insert a node  $n_i$  into a B\*-tree, we randomly choose a node  $n_j$  as its new parent. Then,  $n_i$  is inserted into the left (or right) of  $n_j$  and the original left (or right) child of  $n_j$  becomes the left (or right) child of  $n_i$ . The operation takes O(1) time. According to the above analysis, Op3 takes O(n) time, where

n is the number of modules.

## 5.2 Maintaining a Feasible B\*-tree

The feasibility condition of a B\*-tree may be destroyed after perturbation. Therefore, we shall transform an infeasible B\*-tree into a feasible one after perturbation.

The procedures to transform an infeasible B\*-tree into feasible one are described as follows. For bottom (left) boundary modules, let  $S_b$  ( $S_l$ ) denote the set of the nodes in the leftmost (rightmost) branch in a given B\*-tree. Those nodes corresponding to the bottom (left) boundary modules but are not in  $S_b$  ( $S_l$ ) are recorded in the set  $X_b$  ( $X_l$ ). If  $X_b \neq \emptyset$  ( $X_l \neq \emptyset$ ), each node  $n \in X_b$  ( $n \in X_l$ ) will be deleted from the current position and randomly inserted into the leftmost (rightmost) branch, which takes O(n) time, where n is the number of modules. For example, Figure 10(a) shows an infeasible B\*-tree if node  $n_1$  represents a bottom boundary module but  $n_1 \not\in S_b$ . To get a feasible B\*-tree, we delete  $n_1$  from the B\*-tree and insert it into the leftmost branch. The resulting B\*-tree is shown in Figure 10(b).

For right (top) boundary modules, the procedure to transform an infeasible B\*-tree is a bit more complex than the two procedures described above. Let  $S_r$  ( $S_t$ ) denote the set of the nodes in the bottom-left (bottom-right) branch of a B\*-tree. Let  $X_r$  ( $X_t$ ) denote the set of nodes corresponding to right (top) boundary modules but are not in  $S_r$  ( $S_t$ ). If  $X_r \neq \emptyset$  ( $X_t \neq \emptyset$ ), we delete each node  $n \in X_r$  ( $n \in X_t$ ) from a B\*-tree and insert it into the bottom-left (bottom-right) branch, which takes O(n) time, where n is the number of modules. Further, to guarantee a feasible B\*-tree during perturbation, we do not move nodes to left (right) children of the nodes in the bottom-left (bottom-right) branch.

## **6 Experimental Results**

We implemented our algorithm in the C++ programming language on a 200 MHz SUN Ultra I workstation with 256 MB memory. We compared our algorithm with the sequence-pair based algorithm used in [5] based on the MCNC benchmark circuits listed in Table 1. Columns 1, 2, 3, 4, and 5 in the table give the respective names of circuits, numbers of modules, numbers of top-boundary modules (denoted by T),

Figure 9: An example to delete a node with two children. (a) Node  $n_3$  has two children. (b) The B\*-tree after deleting  $n_3$ .

Figure 10: An example of handling a bottom boundary module. (a) An infeasible  $B^*$ -tree if node  $n_1$  denotes a bottom boundary module but  $n_1$  not in the leftmost branch. (b) A feasible  $B^*$ -tree since  $n_1$  is inserted into the leftmost branch.

| Circuit | # of modules | # of T | # of B | # of L | # of R |

|---------|--------------|--------|--------|--------|--------|

| apte    | 9            | 1      | 1      | 1      | 1      |

| xerox   | 10           | 1      | 1      | 1      | 1      |

| hp      | 11           | 1      | 1      | 1      | 1      |

| ami33   | 33           | 2      | 2      | 2      | 2      |

| ami49   | 49           | 3      | 3      | 2      | 3      |

Table 1: The information of test circuits.

numbers of bottom-boundary modules (denoted by B), numbers of left-boundary modules (denoted by L), and numbers of right-boundary modules (denoted by R). Note that the constrained modules in each circuit are the same as that used in [5] for the purpose of fair comparison.

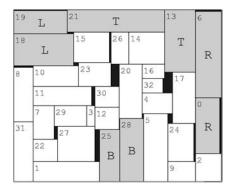

The area and runtime comparisons between the sequence-pair based algorithm [5] and ours are listed in Table 2. (Note that the sequence-pair based algorithm was implemented on a Pentium-II 350 processor with 128MB RAM.) As shown in Table 2, our algorithm results in the average dead space of 15.37%, compared to 18.24% reported by the sequence-pair based algorithm. Also, our algorithm is quite efficient. Figure 11 and Figure 12 show the resulting placements for xerox and ami33 with the boundary-constrained modules shaded.

|         |            | Sequence-Pair  |            |         | B*-tree        |            |         |  |

|---------|------------|----------------|------------|---------|----------------|------------|---------|--|

| Circuit | Total area | resulting area | dead space | runtime | resulting area | dead space | runtime |  |

|         | of modules | $(mm^2)$       | (%)        | (sec)   | $(mm^2)$       | (%)        | (sec)   |  |

| apte    | 46.56      | 46.92          | 0.77       | 15      | 46.92          | 0.77       | 19      |  |

| xerox   | 19.32      | 20.96          | 5.59       | 19      | 19.91          | 3.05       | 22      |  |

| hp      | 8.92       | 9.24           | 3.59       | 23      | 9.27           | 3.92       | 38      |  |

| ami33   | 1.16       | 1.21           | 4.31       | 287     | 1.20           | 3.45       | 144     |  |

| ami49   | 35.43      | 36.84          | 3.98       | 584     | 36.91          | 4.18       | 324     |  |

| Total   |            |                | 18.24      |         |                | 15.37      |         |  |

Table 2: Area and runtime comparisons between the sequence-pair based algorithm (on a Pentium-II 350 PC with 128MB RAM) and our algorithm (on a 200 MHz SUN Ultra I workstation with 256 MB).

Figure 11: The placement result of xerox, where  $T = \{2\}$ ,  $B = \{6\}$ ,  $L = \{8\}$ , and  $R = \{9\}$ . The area is 19.91  $mm^2$ , and the dead space is 3.05 %.

Figure 12: The placement result of ami33, where  $T = \{13, 21\}$ ,  $B = \{25, 28\}$ ,  $L = \{18, 19\}$ , and  $R = \{0, 6\}$ . The area is 1.2  $mm^2$ , and the dead space is 3.45 %.

# 7 Conclusion

We have explored the feasibility conditions of a B\*-tree with boundary constraints and developed a simulated annealing based algorithm using B\*-trees. Also, we have proposed an efficient procedure to transform an infeasible solution into feasible one if the feasibility constraints are violated. Unlike most previous works, our algorithm guarantees a feasible B\*-tree with boundary constraints in each perturbation. Further, our algorithm is very simple and can be implemented easily. And, the operations and packing of B\*-tree take only linear time. Experimental results have shown that our algorithm can obtain smaller silicon area than the most recent work based on sequence pair in less running time.

# References

- [1] Y.-C. Chang, Y.-W. Chang, G.-M. Wu, and S.-W. Wu: 'B\*-Trees: A New Representation for Non-Slicing Floorplans'. 37th Design Automation Conference, DAC'00, June 2000, CA, U.S.A., pp.458–463.

- [2] P.-N. Guo, C.-K. Cheng, and T. Yoshimura: 'An O-Tree Representation of Non-Slicing Floorplan and Its Applications'. 36th Design Automation Conference, DAC'99, June 1999, LA, U.S.A., pp. 268–273.

- [3] X. Hong, G. Huang, T. Cai, J. Gu, S. Dong, C.-K. Cheng, and J. Gu, 'Corner Block List: An effective and efficient topological representation of non-slicing floorplan'. International Conference on Computer Aided Design, ICCAD'00, Nov. 2000, CA, U.S.A, pp. 8–12.

- [4] S. Kirkpatrick, C. D. Gelatt, and M. P. Vecchi: 'Optimization by Simulated Annealing'. *Science*, 1983, **220**, (4598), pp.671–680.

- [5] J. Lai, M.-S. Lin, T.-C. Wang, and Li-C. Wang: 'Module Placement with Boundary Constraints Using the Sequence-Pair Representation'. Asia and South Pacific Design Automation Conference, ASP-DAC'01, Jan. 2001, Yokohama, Japan, pp. 515–520.

- [6] J.-M. Lin and Y.-W. Chang: 'TCG: A Transitive Closure Graph-Based Representation for Non-Slicing Floorplans,' 38th Design Automation Conference, DAC'01, June 2001, NV, U.S.A., pp. 764–769.

- [7] Y. Ma, S. Dong, X. Hong, Y. Cai, C.-K. Cheng, and J. Gu, 'VLSI Floorplanning with Boundary Constraints Based on Corner Block List.' Asia and South Pacific Design Automation Conference, ASP-DAC'01, Jan. 2001, Yokohama, Japan, pp. 509–514.

- [8] H. Murata, K. Fujiyoshi, S. Nakatake, and Y. Kajitani: 'Rectangle-Packing Based Module Placement', International Conference on Computer Aided Design, ICCAD'95, Nov. 1995, CA, U.S.A, pp. 472–479.

- [9] S. Nakatake, K. Fujiyoshi, H. Murata, and Y. Kajitani: 'Module Placement on BSG-Structure and IC Layout Applications', International Conference on Computer Aided Design, ICCAD'96, Nov. 1996, CA, U.S.A., pp. 484–491.

- [10] R. H. J. M. Otten: 'Automatic Floorplan Design', 19th Design Automation Conference, DAC'82, June 1982, U.S.A., pp. 261–267.

- [11] C. H. Papadimitriou and K. Steiglitz: 'Combinatorial Optimization' (Prentice Hall, 1982).

- [12] S. M. Sait, H. Youssef: 'VLSI Physical Design Automation' (McGraw-Hill, 1995).

- [13] X. Tang and D. F. Wong: 'FAST-SP: A fast algorithm for block placement based on sequence pair'. Asia and South Pacific Design Automation Conference, ASP-DAC'01, Jan. 2001, Yokohama, Japan, pp. 521–526.

- [14] T. C. Wang and D. F. Wong: 'An Optimal Algorithm for Floorplan and Area Optimization', 27th Design Automation Conference, DAC'90, June 1990, U.S.A., pp. 180–186.

- [15] D. F. Wong and C. L. Liu: 'A New Algorithm for Floorplan Design'. 23th Design Automation Conference, 23th Design Automation Conference, DAC'86, June 1986, U.S.A., pp. 101–107.

- [16] F. Y. Young and D. F. Wong: 'Slicing Floorplans with Boundary Constraint', Asia and South Pacific Design Automation Conference, ASP-DAC'99, Feb. 1999, Yokohama, Japan, pp. 17–20.

- Fig. 1 A placement with boundary-constrained modules (module  $m_1$  ( $m_2$ ) denotes a left (top) boundary module). (a) An infeasible placement because there exists a module at the left-hand side of  $m_1$ . (b) A feasible placement.

- Fig. 2 (a) A placement. (b) The corresponding B\*-tree.

- Fig. 3 Adding a new module on top, we search the contour from left to right and update it with the top boundary of the new module.

- Fig. 4 (a) The bottom boundary modules. (b) The corresponding nodes in the leftmost branch.

- Fig. 5 (a) The left boundary modules. (b) The corresponding nodes in the rightmost branch.

- Fig. 6 (a) The right boundary modules. (b) The corresponding nodes in the bottom-left branch.

- Fig. 7 (a) The top boundary modules. (b) The corresponding nodes in the bottom-right branch.

- Fig. 8 The flow of our algorithm.

- Fig. 9 An example to delete a node with two children. (a) Node  $n_3$  has two children. (b) The B\*-tree after deleting  $n_3$ .

- Fig. 10 An example of handling a bottom boundary module. (a) An infeasible B\*-tree if node  $n_1$  denotes a bottom boundary module but  $n_1$  not in the leftmost branch. (b) A feasible B\*-tree since  $n_1$  is inserted into the leftmost branch.

- Fig. 11 The placement result of xerox, where  $T = \{2\}$ ,  $B = \{6\}$ ,  $L = \{8\}$ , and  $R = \{9\}$ . The area is 19.91  $mm^2$ , and the dead space is 3.05 %.

- Fig. 12 The placement result of ami33, where  $T = \{13, 21\}$ ,  $B = \{25, 28\}$ ,  $L = \{18, 19\}$ , and  $R = \{0, 6\}$ . The area is 1.2  $mm^2$ , and the dead space is 3.45 %.

- Tab. 1 The information of test circuits.

- Tab. 2 Area and runtime comparisons between the sequence-pair based algorithm (on a Pentium-II 350 PC with 128MB RAM) and our algorithm (on a 200 MHz SUN Ultra I workstation with 256 MB).