# 高遷移率高度垂直堆疊的奈米片／奈米線通道和與二維材料的比較

劉致為

國立臺灣大學電機工程學系

## 摘要

隨著摩爾定律 (Moore's Law) 的發展，電晶體的先進製程邁入全新的 3 奈米與 2 奈米技術節點，具備更高的邏輯密度 (logic density)、更快的速度 (speed)，以及更低的功耗 (power consumption)，可提供高效能運算和行動通訊等應用。為了持續推進未來的技術節點，許多技術上的革新如電晶體架構改變、新穎通道材料、極紫外光微影 (EUV lithography)、先進封裝技術等，全世界各大公司與研發團隊皆投入大量資源進行開發，希望能在競爭激烈的 IC 產業中拔得頭籌。台

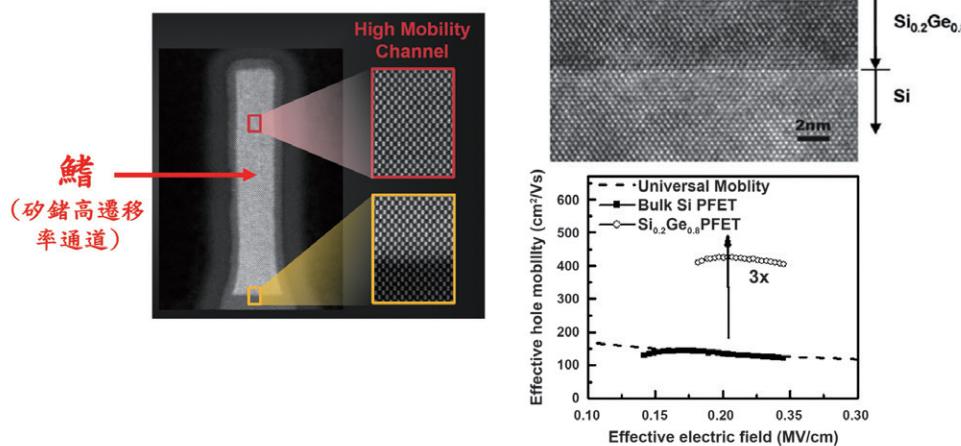

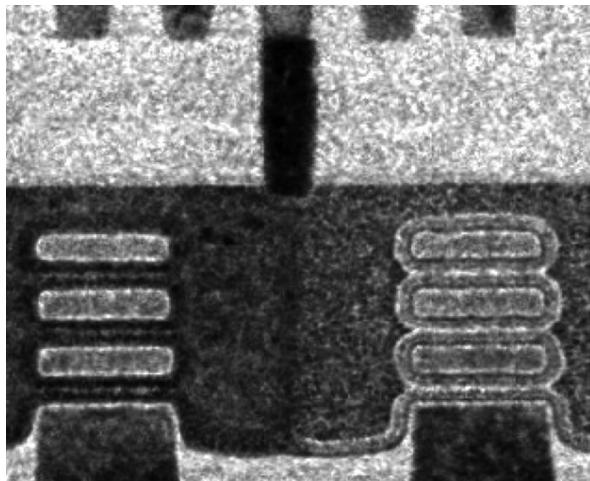

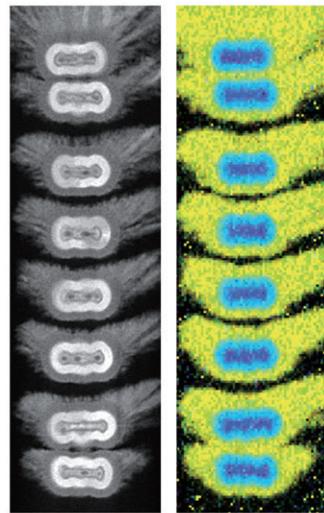

積電自 5 奈米技術節點起採用矽鎵 (SiGe) 高遷移率通道 (high mobility channel) 的鰭式電晶體 (FinFET) 結構 (圖一左) [1, 2]，本研究團隊在 2007 年即證實矽鎵通道的遷移率是矽的三倍，並使用矽覆蓋層 (Si cap) 作為上層的閘極堆疊成長，可增加遷移率 (圖一右) [3]。台積電將在 2 奈米技術節點採用閘極環繞 (gate-all-around, GAA) 的堆疊奈米片電晶體 (stacked nanosheet transistors) 結構 (圖二) [1, 2]，由圖中可看出 N 型與 P 型電晶體的影像明顯不同。在本文中將介紹本研究團隊開發的高遷移率、高度垂直堆疊的奈

圖一 (左) 台積電 5 奈米技術節點的矽鎵高遷移率通道鰭式電晶體 [1, 2]，晶格影像有清楚的啞鈴狀 (dumbbell) 結構 © IEEE。 (右) 具有矽覆蓋層的矽鎵通道，可增加遷移率 [3]。

圖二 台積電 2 奈米技術節點的三層垂直堆疊奈米片電晶體 [1, 2]，N 型電晶體與 P 型電晶體的影像明顯不同。© IEEE

米片 (nanosheet) 與奈米線 (nanowire) 通道電晶體，以增加驅動電流為主要目標，並整合極薄通道 (ultrathin body) 的特性，降低元件的漏電流與次臨界擺幅 (subthreshold swing, SS)，最後與二維材料 (2D material) 電晶體進行比較，以接軌未來產業實際應用。

## 一、緒論

當電晶體的尺寸持續微縮，會產生漏電流變大的問題，為了增加通道的控制能力，電晶體的架構已由傳統的平面電晶體 (Planar FET) 轉變為三維的鰭式電晶體 (FinFET)，台積電從 16 奈米、10 奈米、7 奈米、5 奈米、3 奈米共發展了五代技術節點，為目前主流的元件結構。在更小的技術節點下，需要更進一步抑制短通道效應並增強通道的控制，因此閘極環繞式電晶體 (GAAFET) 將取代鰭式電晶體作為先進技術節點的元件結構，提供更好的閘極控制能力，並提升電晶體的密度。三星 (Samsung) 已宣布於 3 奈米技術節

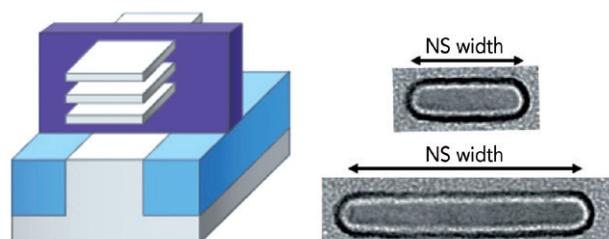

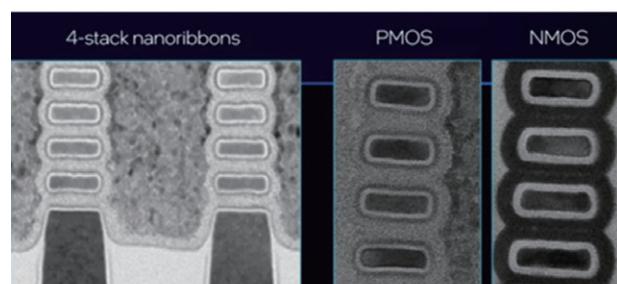

點採用多橋通道電晶體 (Multi-Bridge-Channel FET, MBCFET) 的結構 (圖三) [4, 5]，其與台積電 2 奈米技術節點的堆疊奈米片電晶體 (圖二) 是相似的結構，在通道四周皆被閘極氧化層與閘極金屬完全包覆，形成四面環繞式的閘極結構，可使電晶體有效降低漏電流，更加節能省電。

為了增加電晶體的驅動電流，使半導體晶片效能更高，可採用通道堆疊 (channel stacking) 的技術，往垂直方向堆疊更多通道，增加通道數目，如同建構多層高架橋，在相同占地面積下，可承載更多車流量，使電晶體驅動電流更大，並增加電晶體密度。台積電 2 奈米技術節點使用三層垂直堆疊奈米片電晶體 (圖二)，英特爾 (Intel) 則宣

圖三 三星 3 奈米技術節點的多橋通道電晶體 (左) 示意圖 [4] 與 (右) TEM 影像圖 [5] © IEEE。

圖四 Intel 20A 技術節點的四層垂直堆疊通道電晶體 [6]，N 型及 P 型電晶體影像相似。

圖五 法國半導體研究機構 CEA-Leti 發表的七層垂直堆疊矽通道電晶體 [7]。© IEEE

布 2024 年將以 RibbonFET（垂直堆疊四層的 nanoribbons，也與堆疊奈米片的結構相似）作為 20A 技術節點的結構（圖四）[6]。本研究團隊則突破現有的堆疊技術，研究高遷移率高度垂直堆疊的三維電晶體，包含奈米片（nanosheet）和奈米線（nanowire）通道，最終目標達成 24 層堆疊，大幅超越業界現有的堆疊技術，持續推進技術節點之微縮。

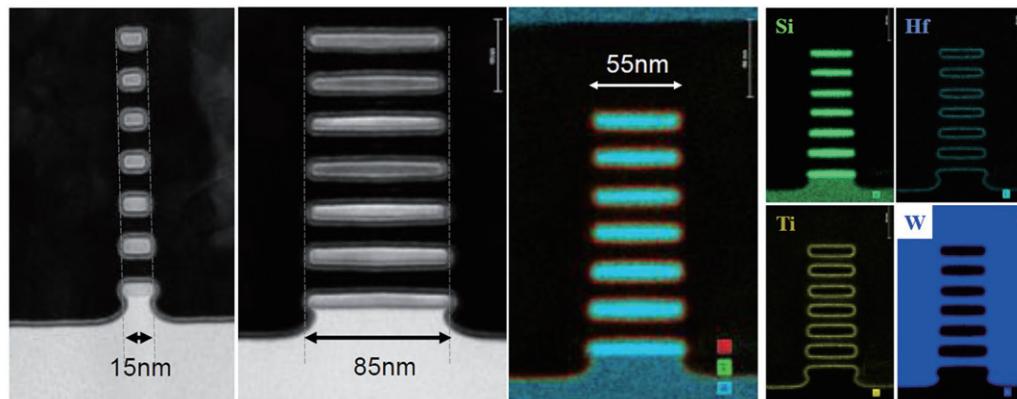

在 2020 年的超大型積體電路設計研討會（Symposium on VLSI Technology, VLSI）中，法國半導體研究機構 CEA-Leti 發表了七層的垂直堆疊矽通道電晶體，利用磊晶（epitaxy）成長  $\text{Si}_{0.7}\text{Ge}_{0.3}/\text{Si}$  的多層結構，並將矽鍺材料作為犧牲層進行選擇性蝕刻（selective etching），最後製備出不同寬度（15 奈米至 85 奈米）的七層堆疊矽奈米片電晶體（圖五）[7]。

## 二、本團隊之研究成果

目前業界和各研究團隊所發表的閘極環繞式電晶體，使用的通道材料大部分以傳統的矽（Si）為主，為了達到更快的電路運作速度，需提升電晶體的總驅動電流（即每一

根垂直堆疊通道電流的總和），除了在相同占地面積下往垂直方向增加通道數目外，採用具有高載子遷移率（mobility）的材料作為電晶體通道，可更進一步提高電晶體的驅動電流。因此本團隊著重於鍺（Ge）、鍺矽（GeSi）、鍺錫（GeSn）等矽基材料的開發，其具有優於矽的載子遷移率，並且與現今業界的矽半導體製程技術有良好的相容性。

### 1. 七層垂直堆疊鍺矽奈米線通道 N 型電晶體

(7 stacked  $\text{Ge}_{0.95}\text{Si}_{0.05}$  nanowire nFET)

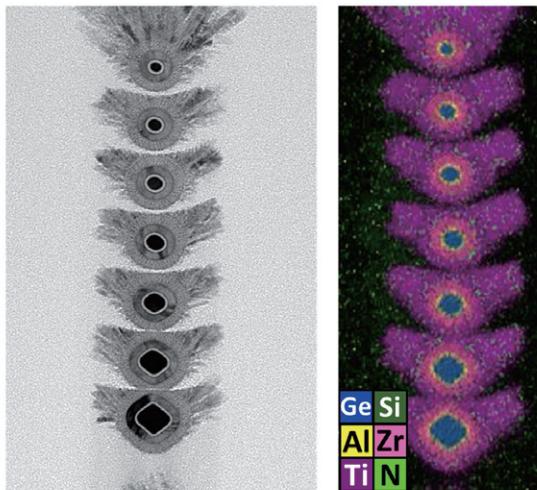

本研究團隊於 2021 年 VLSI 國際會議上展示了世界首顆高效能七層堆疊鍺矽通道奈米線電晶體（圖六）[8]，藉由化學氣相沉積（chemical vapor deposition, CVD）成長鍺濃度為 95% 之鍺矽通道，以提高通道之電子遷移率，並與雙氧水（ $\text{H}_2\text{O}_2$ ）之濕式蝕刻相互優化，成功製備高度垂直堆疊通道之電晶體，並達到鍺／鍺矽三維電晶體驅動電流之世界紀錄。此研究成果也榮獲國際頂尖期刊自然電子學（Nature Electronics）研究亮點（Research Highlight）所報導 [9]。由此可見，高層

圖六 本研究團隊於 2021 VLSI 發表的七層垂直堆疊鍺矽奈米線通道電晶體 [8, 9]。© IEEE

圖七 本研究團隊於 2021 VLSI 發表的八層垂直堆疊鍺矽奈米片通道電晶體 [8]。© IEEE

數垂直堆疊的高遷移率通道電晶體能使電晶體擁有更高的驅動電流，為未來半導體發展的一大趨勢。

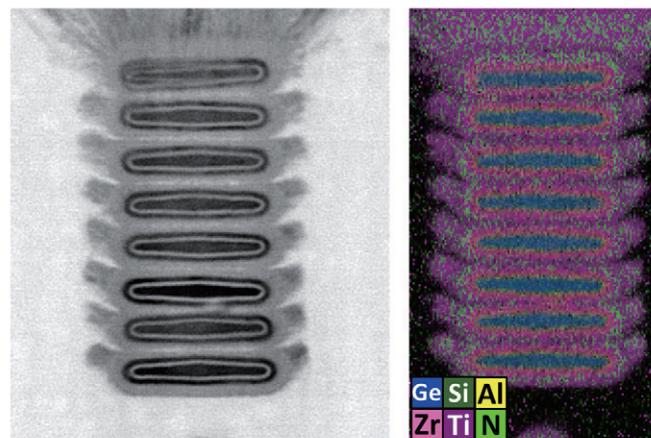

## 2. 八層垂直堆疊鍺矽奈米片通道 N 型電晶體 (8 stacked $\text{Ge}_{0.75}\text{Si}_{0.25}$ nanosheet nFET)

本研究團隊於 2021 年 VLSI 國際會議上同時也展示了世界首顆高層數堆疊鍺矽通道奈米片電晶體（圖七）[8]，達成垂直堆疊層數為八層，且擁有極高的通道均勻性，其堆疊層數已超越法國半導體研究機構 CEA-Leti 發表於 2020 年 VLSI 國際會議的七層垂直堆疊矽通道電晶體（圖五）[7]。藉由不同的蝕刻選擇比（etching selectivity），以及化學氣相沉積磊晶層的設計，可製備出針對不同應用的奈米線或奈米片電晶體。目前臺大乃是業界以外，唯一能研發多層堆疊通道閘極環繞式電晶體的大學，也成為學界與業界接軌的重要橋梁，並以更高層數的垂直堆疊通道電晶體為目標，進行技術突破。

## 3. 八層垂直堆疊鍺錫奈米片極薄通道 P 型 電晶體 (8 stacked $\text{Ge}_{0.9}\text{Sn}_{0.1}$ ultrathin body pFETs)

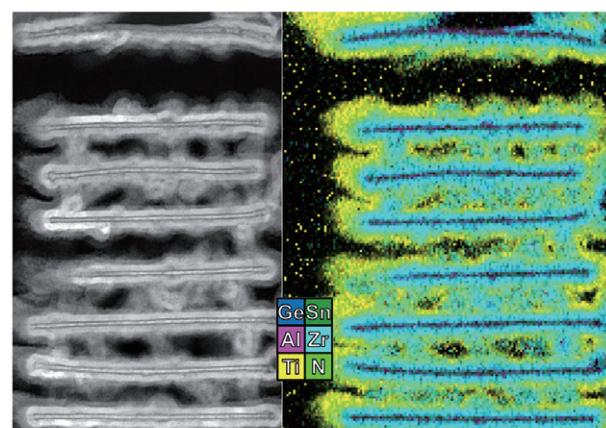

P 型電晶體方面，本研究團隊在 2021 年國際電子元件會議（International Electron Devices Meeting, IEDM）上展示世界首顆八層垂直堆疊鍺錫奈米片極薄通道電晶體（圖八）[10]，以高電洞遷移率的鍺錫通道材料，搭配

圖八 本研究團隊於 2021 IEDM 發表的八層垂直堆疊鍺錫奈米片極薄通道電晶體 [10]。© IEEE

圖九 本研究團隊於 2022 VLSI 發表的均匀八層垂直堆疊鎗錫奈米片極薄通道電晶體，達到 64 mV/dec 的次臨界擺幅 [11]。© IEEE

優化的磊晶層設計與高選擇比等向性乾蝕刻 (highly selective isotropic dry etching, HiSIDE) 製程，成功製備出厚度為 3 奈米之極薄通道。因量子侷限效應 (quantum confinement effect) 的影響，能有效降低元件之漏電流，提升開關電流比 ( $I_{ON}/I_{OFF}$ )。此篇論文也獲得 2021 年 IEDM 最佳學生論文獎 (Roger A. Haken Best Student Paper Award)，為台灣

首度獲得此獎項。於 2022 年 VLSI 國際會議上，本團隊更進一步發表了開關電流比與次臨界擺幅 (subthreshold swing, SS) 皆為世界紀錄的八層堆疊鎗錫極薄通道電晶體 (圖九) [11]，其平均通道厚度 (body thickness,  $T_{body}$ ) 為 2.4 奈米，達成極低的次臨界擺幅 (64 mV/dec)，優於台積電量產之 5 奈米矽鎗高遷移率通道鱗式電晶體 (69 mV/dec [12])。

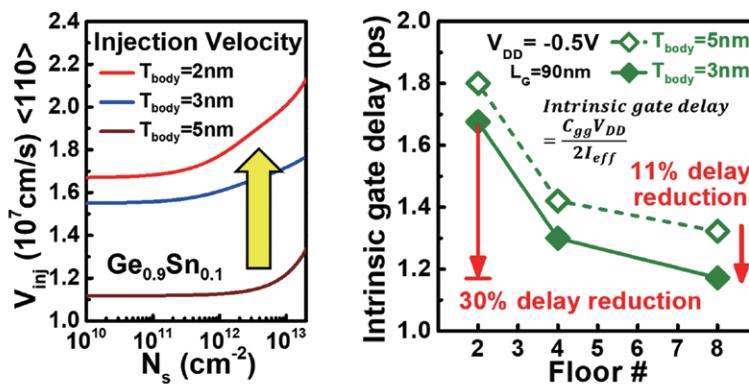

#### 4. 利用高遷移率高度垂直堆疊的奈米片極薄通道增加注入速度 (injection velocity) 與減少延遲 (delay)

除了極高的開關電流比和極低的次臨界擺幅之外，極薄通道也有助於提升注入速度 (injection velocity,  $V_{inj}$ ) 以增強短通道元件的性能。藉由 TCAD 模擬不同鎗錫通道厚度的電洞注入速度，可得注入速度隨著通道厚度的下降而增加 (圖十左) [11]。此外，也以 TCAD 模擬不同堆疊通道層數 (floor number) 的 5 奈米通道及 3 奈米極薄通道的閘極延遲 (intrinsic gate delay) (圖十右) [11]。在八層垂直堆疊的情況下，3 奈米極薄通道較

圖十 (左) 電洞注入速度 ( $V_{inj}$ ) 與 (右) 閘極延遲對堆疊通道層數之關係 [11]。高遷移率高度垂直堆疊的極薄通道可提升注入速度並減少延遲。© IEEE

5 奈米可減少 11% 的延遲；八層垂直堆疊的極薄通道（3 奈米）相較於二層則可減少 30% 的延遲。由此可見，高遷移率、高度垂直堆疊的奈米片極薄通道可有效提升注入速度，並減少閘極延遲，為短通道元件發展的重要方向。

### 三、與二維材料的比較

上述的鍺矽（GeSi）與鍺錫（GeSn）等四族矽基材料，具有高載子遷移率的特性，可增加電晶體的驅動電流，並且其製程技術與目前的鰭式電晶體及堆疊奈米片／奈米線

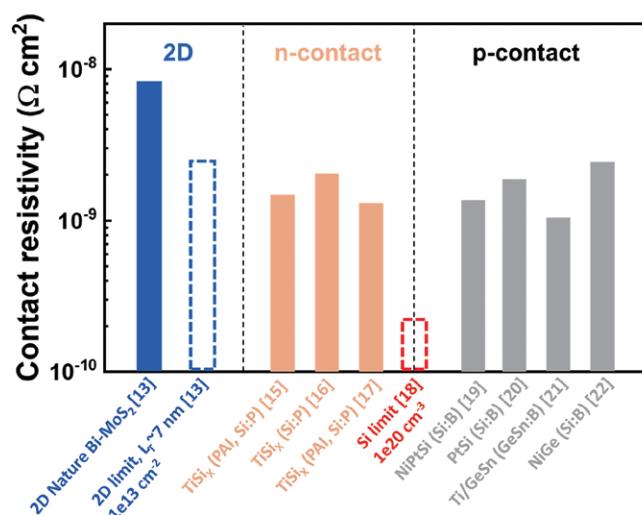

電晶體有良好的相容性，具有成為下世代通道材料的潛力。其他非矽基的新穎材料，如二維材料（2D Material）等也是近年來被廣泛研究的題目，因為其單層原子的特性，許多人認為是摩爾定律繼續微縮的可能候選之一，在自然期刊（Nature）[13] 以及 IEDM 國際會議 [14] 上皆有相關的論文探討。然而，二維材料面臨了大面積高品質的晶圓成長技術挑戰，且目前業界尚無量產設備。此外，二維材料具有高接觸電阻率（約  $10^{-8} \Omega \cdot \text{cm}^2$ ，矽基約  $10^{-9} \Omega \cdot \text{cm}^2$ ）（圖十一）、低電流（表一）等

圖十一 矽基材料與二維材料接觸電阻率（contact resistivity）之比較。二維材料的接觸電阻率（約  $10^{-8} \Omega \cdot \text{cm}^2$ ）較矽基材料（約  $10^{-9} \Omega \cdot \text{cm}^2$ ）高。

表一 矽基材料（藍框）與二維材料（紅框）之比較。二維材料電晶體的驅動電流（ $I_{ON}$ ）遠小於矽基電晶體。

| Reference                                        | nFET                                                              |                                                               |                                                                               | pFET                                                              |                                                                    |                                                                            |

|--------------------------------------------------|-------------------------------------------------------------------|---------------------------------------------------------------|-------------------------------------------------------------------------------|-------------------------------------------------------------------|--------------------------------------------------------------------|----------------------------------------------------------------------------|

|                                                  | VLSI 2021 (NTU) [8]                                               | Nature 2021 (MIT) [13]                                        | EDL 2021 (NTU) [23]                                                           | IEDM 2021 (NTU) [10]                                              | IEDM 2021 (NTU) [10]                                               | IEDM 2021 (Intel) [14]                                                     |

| Channel                                          | 7 stacked $\text{Ge}_{0.95}\text{Si}_{0.05}$ nanowires            | MoS₂                                                          | MoS₂                                                                          | 8 stacked $\text{Ge}_{0.9}\text{Sn}_{0.1}$ ultrathin bodies       | 8 stacked $\text{Ge}_{0.9}\text{Sn}_{0.1}$ thick nanosheets        | WSe₂                                                                       |

| $I_{ON}$ at $V_{DS} = \pm 0.5\text{V}/1\text{V}$ | 4100 $\mu\text{A}/\mu\text{m}$ at $V_{OV} = V_{DS} = 0.5\text{V}$ | 42 $\mu\text{A}/\mu\text{m}$ at $V_{OV} = V_{DS} = 1\text{V}$ | 480 $\mu\text{A}/\mu\text{m}$ at $V_{GS} = 30\text{V}$ , $V_{DS} = 1\text{V}$ | 290 $\mu\text{A}/\mu\text{m}$ at $V_{OV} = V_{DS} = -0.5\text{V}$ | 1500 $\mu\text{A}/\mu\text{m}$ at $V_{OV} = V_{DS} = -0.5\text{V}$ | 50 $\mu\text{A}/\mu\text{m}$ at $V_G = -4\text{V}$ , $V_{DS} = -1\text{V}$ |

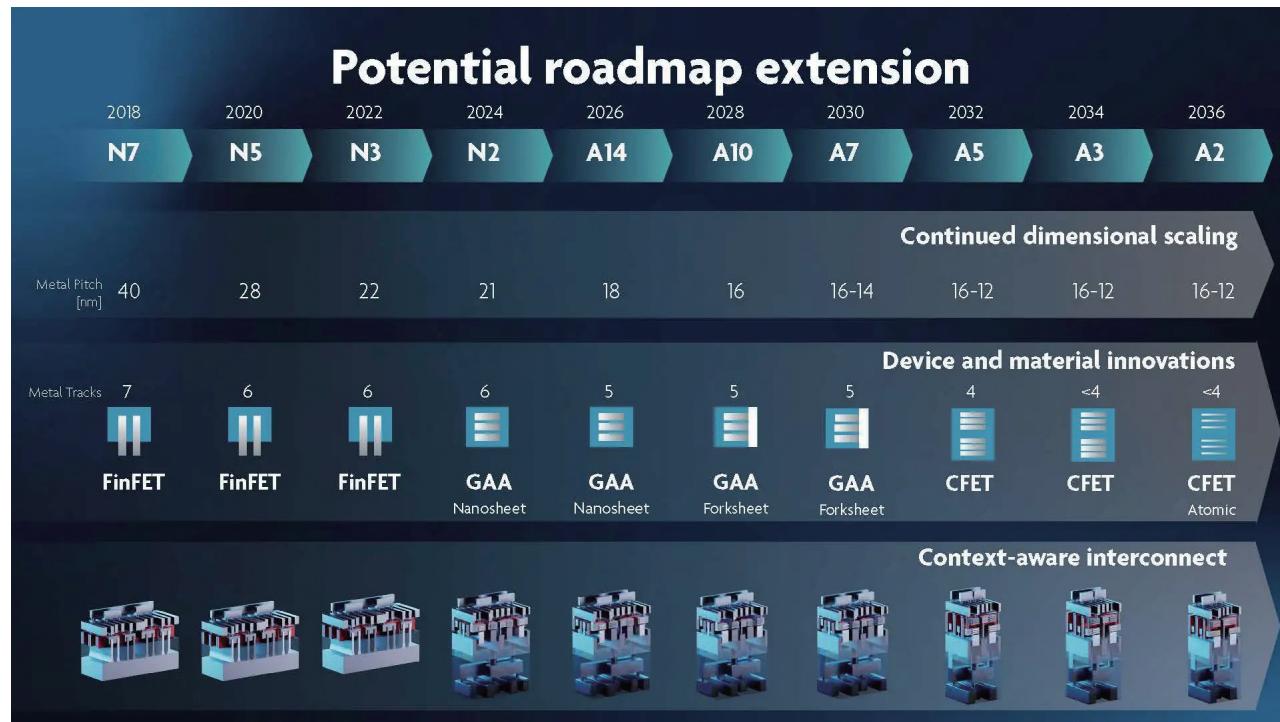

圖十二 IMEC 最新發表的電晶體 roadmap [24]，預期在 A5 和 A2 節點分別採用 CFET 和 atomic channel 的結構

諸多問題。二維材料在元件製程上難以與業界成熟之矽基材料或鰭式電晶體／奈米片／奈米線等三維電晶體結構相容，在元件效能的表現上也較矽基電晶體有差距，目前離量產仍十分遙遠，需要繼續努力。

根據比利時校際微電子中心（IMEC）發表最新的 technology roadmap（圖十二）[24]，下一個技術節點（N2）的電晶體結構將由鰭式電晶體轉變為閘極環繞式的奈米片電晶體（2024 年），接著引入互補式場效電晶體（complementary FET, CFET）結構，在 A5 技術節點（2032 年）將兩個電晶體進行垂直堆疊，相較於通道的垂直堆疊，可更進一步減少占地面積。此外依據 roadmap 預測，

在 2036 年的 A2 技術節點將搭配原子層通道（atomic channels），因此本研究團隊所研發的極薄通道，將厚度持續微縮至 1 奈米，可作為原子層通道的材料，具有高遷移率及高注入速度以提升驅動電流，並藉由量子侷限的特性來降低漏電流。至於二維材料的重要性可能在十年甚至十五年之後，且須先以實驗證明較矽基材料好，才有機會應用於電晶體的量產。

#### 四、結論

本研究團隊整合高層數、高遷移率，以及極薄通道的特性，成功製備高遷移率高度垂直堆疊的奈米片／奈米線通道電晶體，提升驅動電流並降低漏電流，可使半導體晶片

效能更高，並且更加省電。二維材料與矽基材料相比，若要量產仍需克服許多挑戰。■

## 【參考文獻】

- [1] Mark Liu, “Unleashing the Future of Innovation,” 2021 IEEE International Solid-State Circuits Conference (ISSCC), Plenary Session 1.1, 2021.

- [2] Yuh-Jier Mii, “Semiconductor Innovation: From Device to System,” IEEE Symposium on VLSI Technology and Circuits (VLSI), pp. 276-281, 2022.

- [3] C.-Y. Peng et al., “Hole mobility enhancement of  $\text{Si}_{0.2}\text{Ge}_{0.8}$  quantum well channel on Si,” Applied Physics Letters, Vol. 90, No. 1, pp. 012114-1-012114-3, 2007.

- [4] Samsung Newsroom, “Samsung Electronics’ Leadership in Advanced Foundry Technology Showcased with Latest Silicon Innovations and Ecosystem Platform,” [Online] <https://news.samsung.com/global/samsung-electronics-leadership-in-advanced-foundry-technology-showcased-with-latest-silicon-innovations-and-ecosystem-platform>

- [5] G. Bae et al., “3nm GAA Technology featuring Multi-Bridge-Channel FET for Low Power and High Performance Applications,” IEEE International Electron Devices Meeting (IEDM), pp. 656-659, 2018.

- [6] Pat Gelsinger, “Intel Accelerated” [Online] <https://download.intel.com/newsroom/2021/client-computing/Intel-Accelerated-2021-presentation.pdf>

- [7] S. Barraud et al., “7-Levels-Stacked Nanosheet GAA Transistors for High Performance Computing,” IEEE Symposia on VLSI Technology and Circuits (VLSI), TC1.2, 2020.

- [8] Y.-C. Liu et al., “First Highly Stacked  $\text{Ge}_{0.95}\text{Si}_{0.05}$  nGAAFETs with Record  $I_{ON} = 110 \mu\text{A}$  ( $4100 \mu\text{A}/\mu\text{m}$ ) at  $V_{OV}=V_{DS}=0.5\text{V}$  and High  $G_{m,max} = 340 \mu\text{S}$  ( $13000 \mu\text{S}/\mu\text{m}$ ) at  $V_{DS}=0.5\text{V}$  by Wet Etching,” IEEE Symposia on VLSI Technology and Circuits (VLSI), T15-2, 2021.

- [9] S. Thomas, “Germanium nanowire transistors stack up,” Nature Electronics, Vol. 4, July 2021, 452.

- [10] C.-E. Tsai et al., “Highly Stacked 8  $\text{Ge}_{0.9}\text{Sn}_{0.1}$  Nanosheet pFETs with Ultrathin Bodies ( $\sim 3\text{nm}$ ) and Thick Bodies ( $\sim 30\text{nm}$ ) Featuring the Respective Record  $I_{ON}/I_{OFF}$  of  $1.4 \times 10^7$  and Record  $I_{ON}$  of  $92 \mu\text{A}$  at  $V_{OV}=V_{DS} = -0.5\text{V}$  by CVD Epitaxy and Dry Etching,” IEEE International Electron Devices Meeting (IEDM), pp. 569-572, 2021.

- [11] C.-E. Tsai et al., “Nearly Ideal Subthreshold Swing and Delay Reduction of Stacked Nanosheets Using Ultrathin Bodies,” IEEE Symposium on VLSI Technology and Circuits (VLSI), pp. 401-402, 2022.

- [12] G. Yeap et al., “5nm CMOS Production Technology Platform featuring full-fledged EUV, and High Mobility Channel FinFETs with densest  $0.021 \mu\text{m}^2$  SRAM cells for Mobile SoC and High Performance Computing Applications,” IEEE International Electron Devices Meeting (IEDM), pp. 879-882, 2019.

- [13] P.-C. Shen et al., “Ultralow contact resistance between semimetal and monolayer semiconductors,” Nature, 593, 211-217, 2021.

- [14] K. P. O’Brien et al., “Advancing 2D Monolayer CMOS Through Contact, Channel and Interface Engineering,” IEEE International Electron Devices Meeting (IEDM), pp. 146-149, 2021.

- [15] H. Yu et al., “Titanium Silicide on Si:P With Pre-contact Amorphization Implantation Treatment: Contact Resistivity Approaching  $1 \times 10^{-9} \text{ Ohm-cm}^2$ ,” IEEE Transactions on Electron Devices, Vol. 63, No. 12, pp. 4632-4641, 2016.

- [16] E. Rosseel et al., "Contact Resistivity of Highly Doped Si:P, Si:As, and Si:P:As Epi Layers for Source/Drain Epitaxy," *ECS Transactions*, Vol. 98, No. 5, pp. 37-42, 2020.

- [17] C.-N. Ni et al., "Ultra-low NMOS contact resistivity using a novel plasma-based DSS implant and laser anneal for post 7 nm nodes," *IEEE Symposia on VLSI Technology and Circuits (VLSI)*, 2016.

- [18] J. Maassen et al., "Full band calculations of the intrinsic lower limit of contact resistivity," *Applied Physics Letters*, Vol. 102, No. 11, pp. 111605-1-111605-4, 2013.

- [19] Z. Zhang et al., "Sharp Reduction of Contact Resistivities by Effective Schottky Barrier Lowering With Silicides as Diffusion Sources," *IEEE Electron Device Letters*, Vol. 31, No. 7, pp. 731-733, 2010.

- [20] N. Stavitski et al., "Systematic TLM Measurements of NiSi and PtSi Specific Contact Resistance to n- and p-Type Si in a Broad Doping Range," *IEEE Electron Device Letters*, Vol. 29, No. 4, pp. 378-381, 2008.

- [21] C.-E. Tsai et al., "Low Contact Resistivity to Ge Using In-Situ B and Sn Incorporation by Chemical Vapor Deposition," *IEEE Transactions on Electron Devices*, Vol. 67, No. 11, pp. 5053-5058, 2020.

- [22] H. Miyoshi et al., "In-situ contact formation for ultra-low contact resistance NiGe using carrier activation enhancement (CAE) techniques for Ge CMOS," *IEEE Symposia on VLSI Technology and Circuits (VLSI)*, 2014.

- [23] A.-S. Chou et al., "High On-State Current in Chemical Vapor Deposited Monolayer MoS<sub>2</sub> nFETs With Sn Ohmic Contacts," *IEEE Electron Device Letters*, Vol. 42, No. 2, pp. 272-275, 2021.

- [24] IMEC, Future Summits 2022.