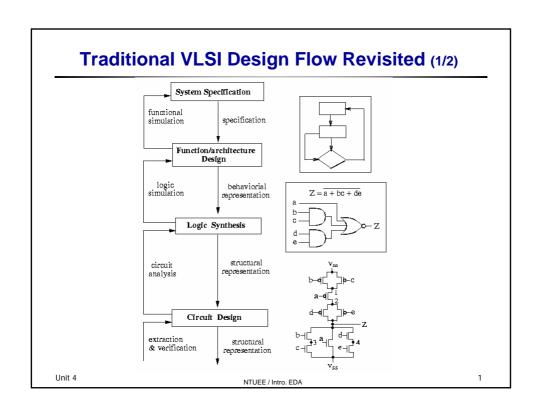

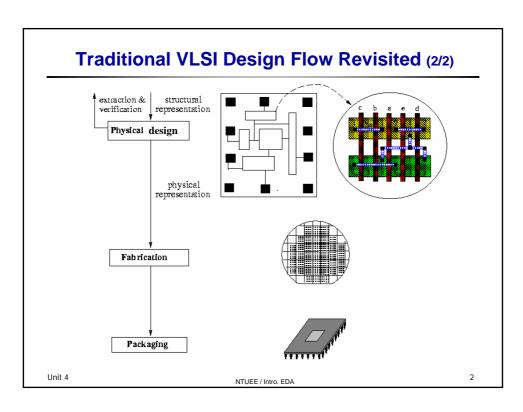

# **Physical Design**

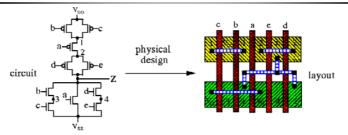

- Physical design converts a circuit description into a geometric description.

- The description is used to manufacture a chip.

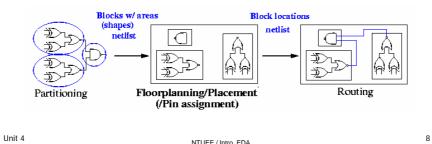

- Physical design cycle:

- Logic partitioning

- 2. Floorplanning and placement

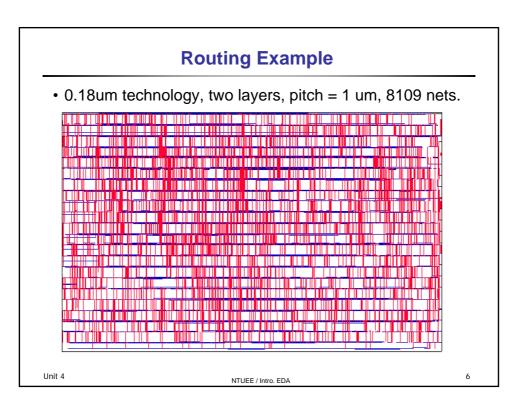

- 3. Routing

- 4. Compaction

- Others: circuit extraction, timing verification, and design rule checking

Unit 4 NTUEE / Intro. EDA

# Physical Design Puritioning Placement Routing Compaction Extraction & Physical Design Placement A routing system Little Market Market

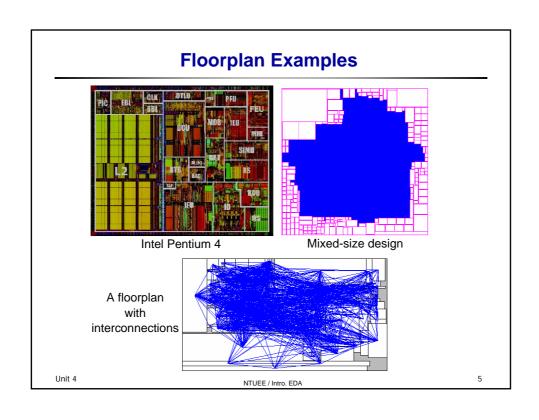

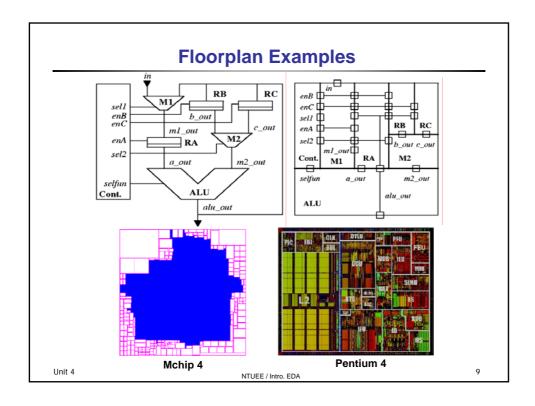

# **Floorplanning**

- Course contents

- Floorplanning basics

- Normalized Polish expression for slicing flooprlans

- B\*-trees for non-slicing floorplans

- Readings

- Chapters 8 and 5.6

PowerPC 604

Pentium 4

Unit 4

NTUEE / Intro. EDA

### **Floorplanning**

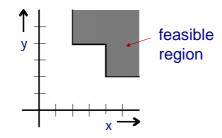

- Partitioning leads to

- Blocks with well-defined areas and shapes (rigid/hard blocks).

- Blocks with approximate areas and no particular shapes (flexible/soft blocks).

- A netlist specifying connections between the blocks.

- Objectives

- Find locations for all blocks.

- Consider shapes of soft block and pin locations of all the blocks.

# **Early Layout Decision Methodology**

- An IC is a 2-D medium; considering the dimensions of blocks in early stages of the design helps to improve the quality.

- Floorplanning gives early feedback

- Suggests valuable architectural modifications

- Estimates the whole chip area

- Estimates delay and congestion due to wiring

- Floorplanning fits very well in a *top-down* design strategy; the *step-wise refinement* strategy also propagated in software design.

- Floorplanning considers the *flexibility* in the shapes and terminal locations of blocks.

Unit 4 NTUEF / Intro. EDA 10

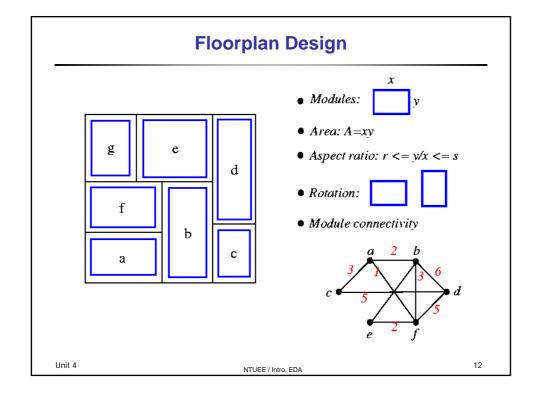

- Inputs to the floorplanning problem:

- A set of blocks, hard or soft.

- Pin locations of hard blocks.

- A netlist.

- Objectives: minimize area, reduce wirelength for (critical) nets, maximize routability (minimize congestion), determine shapes of soft blocks, etc.

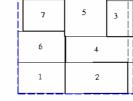

An optimal floorplan, in terms of area

A non-optimal floorplan

Unit 4

NTUEE / Intro. EDA

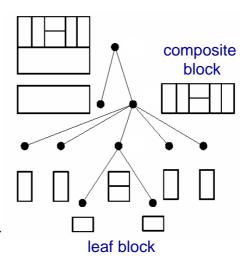

### **Floorplan Elements**

- Leaf block (cell/module): a block at the lowest level of the hierarchy; it does not contain any other block.

- Composite block

(cell/module): a block

that is composed of

either leaf blocks or

composite blocks. The

entire IC is the highest level composite block.

Unit 4 NTUEE / Intro. EDA 13

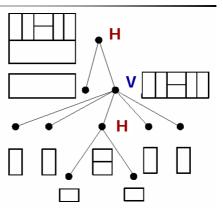

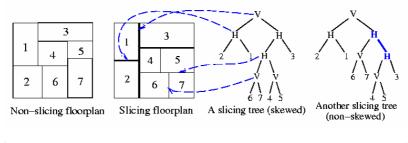

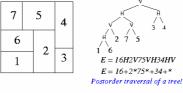

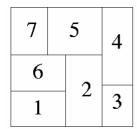

# Slicing Floorplan + Slicing Tree

- A composite block's subblocks are obtained by a horizontal or vertical bisection of the composite block.

- Slicing floorplans can be represented by a slicing tree.

- In a slicing tree, all blocks (except for the top-level block) have a parent, and all composite blocks have children.

- A slicing floorplan is also called a floorplan of order 2.

H: horizontal cut V: vertical cut different from the definitions in the text!!

Unit 4 NTLIEF / Intro. FDA 14

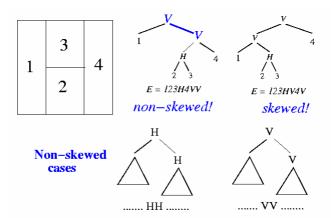

# **Skewed Slicing Tree**

- Rectangular dissection: Subdivision of a given rectangle by a finite # of horizontal and vertical line segments into a finite # of nonoverlapping rectangles.

- Slicing structure: a rectangular dissection that can be obtained by repetitively subdividing rectangles horizontally or vertically.

- Slicing tree: A binary tree, where each internal node represents a vertical cut line or horizontal cut line, and each leaf a basic rectangle.

- **Skewed slicing tree:** One in which no node and its **right** child are the same.

Unit 4 NTUEE / Intro. EDA

# Floorplan Design by Simulated Annealing

- Slicing Floorplan: Wong & Liu, "A new algorithm for floorplan design," DAC-86.

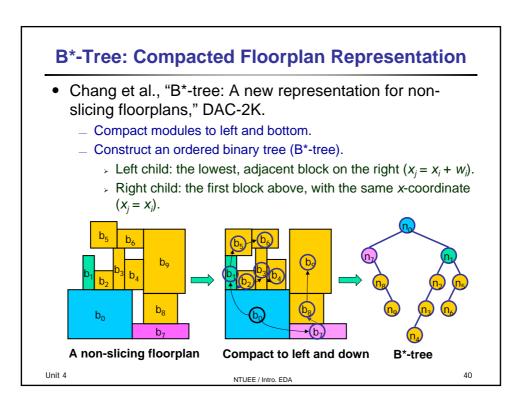

- Compacted Floorplan: Chang, Chang, Wu, and Wu, "B\*-tree: A new representation for non-slicing floorplans," DAC-2K.

- Kirkpatrick, Gelatt, and Vecchi, "Optimization by simulated annealing," *Science*, May 1983.

Unit 4 NTUEE / Intro. EDA 16

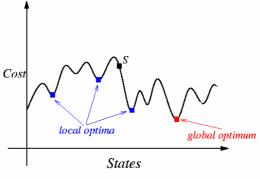

### **Simulated Annealing Basics**

- Non-zero probability for "up-hill" moves.

- Probability depends on

- 1. magnitude of the "up-hill" movement

- 2. total search time

$$Prob(S \to S') = \begin{cases} 1 & \text{if } \Delta C \le 0 \text{ } /* \text{ "down-hill" moves * / } \\ e^{-\Delta C} & \text{if } \Delta C > 0 \text{ } /* \text{ "up-hill" moves * / } \end{cases}$$

- $\Delta C = cost(S') Cost(S)$

- *T*: Control parameter (temperature)

- Annealing schedule:  $T=T_0$ ,  $T_1$ ,  $T_2$ , ..., where  $T_i=r^i$   $T_0$ , r<1.

Unit 4 NTLIEF / letro EDA 17

### **Generic Simulated Annealing Algorithm**

```

1 begin

2 Get an initial solution S;

3 Get an initial temperature T > 0;

4 while not yet "frozen" do

5 for 1 \le i \le P do

6 Pick a random neighbor S' of S;

7 \Delta \leftarrow cost(S') - cost(S);

/* downhill move */

8 if \Delta \le 0 then S \leftarrow S'

/* uphill move */

9 if \Delta > 0 then S \leftarrow S' with probability e^{-\frac{\Delta}{T}};

10 T \leftarrow rT; /* reduce temperature */

11 return S

12 end

```

Unit 4 NTLIEF / Intro. EDA 18

### **Basic Ingredients for Simulated Annealing**

Analogy:

| Physical system   | Optimization problem  |

|-------------------|-----------------------|

| state             | configuration         |

| energy            | cost function         |

| ground state      | optimal solution      |

| quenching         | iterative improvement |

| careful annealing | simulated annealing   |

- Basic Ingredients for Simulated Annealing:

- Solution space

- Neighborhood structure

- Cost function

- Annealing schedule

Unit 4 NTUEE / Intro. EDA

19

20

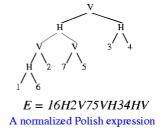

# **Solution Representation: Slicing Flooprlan**

- An expression  $E = e_1 e_2 \dots e_{2n-1}$ , where  $e_i \in \{1, 2, \dots, n, H, V\}$ ,  $1 \le i \le 2n-1$ , is a **Polish expression** of length 2n-1 iff

- every operand j,  $1 \le j \le n$ , appears exactly once in E;

- 2. **(the balloting property)** for every subexpression  $E_i = e_1 \dots e_j$ ,  $1 \le i \le 2n-1$ , # operands > # operators.

- Polish expression ↔ Postorder traversal.

- *ijH*: rectangle *i* on bottom of *j*; *ijV*: rectangle *i* on the left of *j*.

Unit 4

# **Redundant Representations**

• Question: How to eliminate ambiguous representation?

Unit 4 NTUEE / Intro. EDA 21

# **Normalized Polish Expression**

- A Polish expression E = e<sub>1</sub> e<sub>2</sub> ... e<sub>2n-1</sub> is called normalized iff E has no consecutive operators of the same type (H or V).

- Given a normalized Polish expression, we can construct a unique rectangular slicing structure.

Unit 4 NTUEF / Intro EDA 22

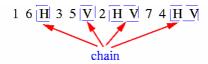

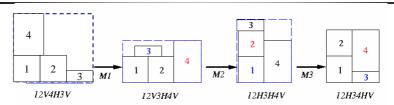

### **Neighborhood Structure**

• Chain: HVHVH ... or VHVHV ...

- Adjacent: 1 and 6 are adjacent operands; 2 and 7 are adjacent operands; 5 and V are adjacent operand and operator.

- 3 types of moves:

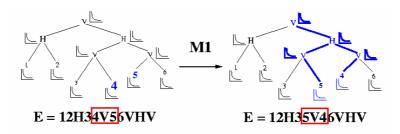

- M1 (Operand Swap): Swap two adjacent operands.

- -M2 (**Chain Invert**): Complement some chain (V = H, H = V).

- M3 (Operator/Operand Swap): Swap two adjacent operand and operator.

Unit 4 NTUEE / Intro. EDA 23

### **Effects of Perturbation**

- Question: The balloting property holds during the moves?

- M1 and M2 moves are OK.

- Check the M3 moves! Reject "illegal" M3 moves.

- Check M3 moves: Assume that M3 swaps the operand  $e_i$  with the operator  $e_{i+1}$ ,  $1 \le i \le k-1$ . Then, the swap will not violate the balloting property iff  $2N_{i+1} < i$ .

- $-N_k$ : # of operators in the Polish expression  $E = e_1 e_2 ... e_k$ , 1 ≤  $k \le 2n$ -1

Unit 4 NTUEE / Intro. EDA 24

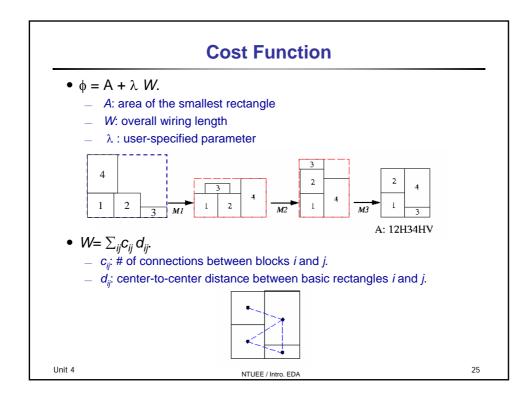

# **Incremental Computation of Cost Function**

- Each move leads to only a minor modification of the Polish expression.

- At most **two paths** of the slicing tree need to be updated for each move.

Unit 4 NTUEE / Intro. EDA 27

# Incremental Computation of Cost Function (cont'd) E = 12H34V56VHV E = 12H34V56VHV E = 12H34V56VHV Unit 4

### **Annealing Schedule**

• Initial solution: 12 V3 V ... nV.

- $T_i = r^i T_0$ , i = 1, 2, 3, ...; r = 0.85.

- At each temperature, try kn moves (k = 5-10).

- Terminate the annealing process if

- # of accepted moves < 5%,</p>

- temperature is low enough, or

- run out of time.

Unit 4 29 NTUEE / Intro. EDA

```

Algorithm: Wong-Liu (P, \epsilon, r, k)

```

```

1 begin 2 E \leftarrow 12V3V4V ... nV; /* initial solution */ 3 Best \leftarrow E; T_0 \leftarrow \frac{\Sigma_{avg}}{ln(P)}; M \leftarrow MT \leftarrow uphill \leftarrow 0; N = kn; 4 repeat

MT \leftarrow \text{uphill} \leftarrow \text{reject} \leftarrow 0;

SelectMove(M);

Case M of

Case M of M_1: Select two adjacent operands e_i and e_j: NE \leftarrow \text{Swap}(E, e_i, e_j); M_2: Select a nonzero length chain C; NE \leftarrow \text{Complement}(E, C); M_3: done \leftarrow \text{FALSE}; while not (done) do Select two adjacent operand e_i and operator e_{i+1}; if (e_{i+1} \neq e_{i+1}) and (2 N_{i+1} < i) then done \leftarrow \text{TRUE}; Select two adjacent operator e_i and operand e_{i+1}; if (e_i \neq e_i) then done \leftarrow \text{TRUE}:

10

12

13

14

13

if (e \neq e_{i+2}) then done \leftarrow TRUE;

NE \leftarrow Swap(E, e_i, e_{i+1});

MT \leftarrow MT+1; \Delta cost \leftarrow cost(NE) - cost(E);

if (\Delta cost \leq 0) or (Random < \underbrace{-\Delta cost}_{e}) then

15

16

17

18

if (\triangle cost > 0) then uphill \leftarrow uphill + 1;

19

E \leftarrow NE; if cost(E) < cost(best) then best \leftarrow E;

20

else reject ← reject + 1;

until (uphill > N) or (MT > 2N);

T \leftarrow rT; /* reduce temperature */

25 until (reject/MT > 0.95) or (T < \varepsilon) or OutOfTime;

26 end

Unit 4

30

NTUEE / Intro. EDA

```

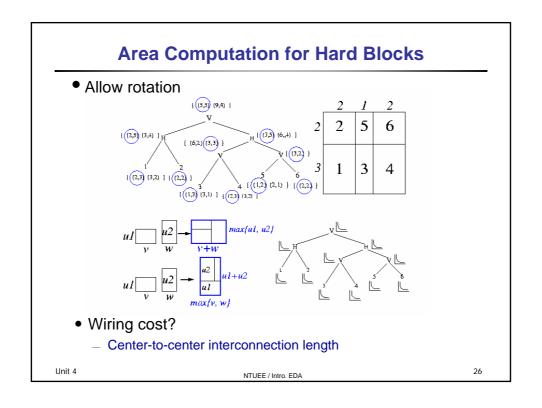

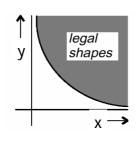

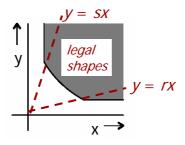

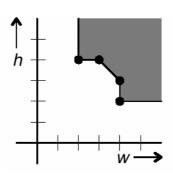

### **Shape Curve for Floorplan Sizing**

- A soft (flexible) block *b* can have different aspect ratios, but is with a fixed area *A*.

- The shape function of *b* is a hyperbola: xy = A, or y = AIx, for width *x* and height *y*.

- Very thin blocks are often not interesting and feasible to design; add two straight lines for the constraints on aspect ratios.

- Aspect ratio:  $r \le y/x \le s$ .

Unit 4

NTUEE / Intro. EDA

### **Shape Curve**

- Since a basic block is built from discrete transistors, it is not realistic to assume that the shape function follows the hyperbola continuously.

- In an extreme case, a block is rigid/hard: it can only be rotated and mirrored during floorplanning or placement.

The shape curve of a  $2 \times 4$  hard block.

Unit 4

NTUEE / Intro. ED

32

# **Shape Curve (cont'd)**

- In general, a *piecewise linear* function can be used to approximate any shape function.

- The points where the function changes its direction, are called the corner (*break*) *points* of the piecewise linear function.

Unit 4

NTUEE / Intro. EDA

33

34

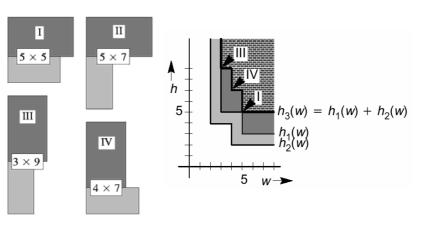

### **Vertical Abutment**

Composition by vertical abutment (horizontal cut) ⇒ the addition of shape functions.

Unit 4

TUEE / Intro. EDA

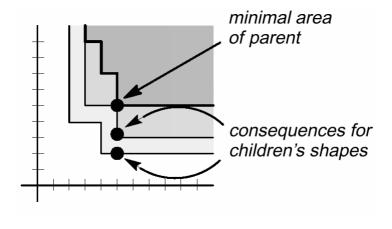

### **Deriving Shapes of Children**

A choice for the minimal shape of a composite block fixes the shapes of the shapes of its children blocks.

Unit 4 NTUEE / Intro. EDA 3

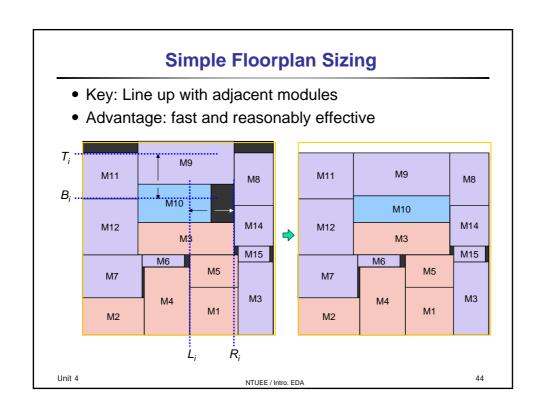

# **Slicing Floorplan Sizing**

- The shape functions of all leaf blocks are given as piecewise linear functions.

- Traverse the slicing tree to compute the shape functions of all composite blocks (bottom-up composition).

- Choose the desired shape of the top-level block; as the shape function is piecewise linear only the corner points of the function need to be evaluated, when looking for the minimal area.

- Propagate the consequences of the choice down to the leaf blocks (top-down propagation).

- The sizing algorithm runs in polynomial time for slicing floorplans

- NP-complete for non-slicing floorplans

Unit 4 NTLIEF / Intro. EDA 36

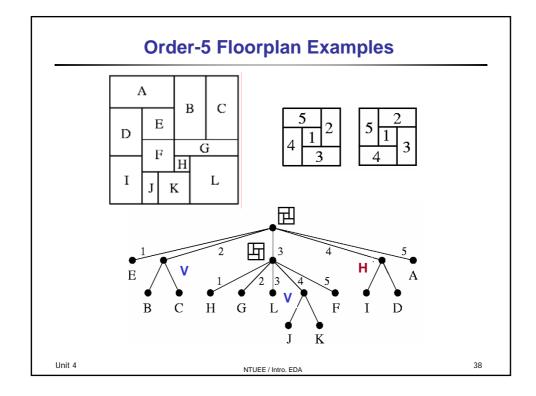

# Wheel or Spiral Floorplan

- This floorplan is not slicing!

- Wheel is the smallest non-slicing floorplans.

- Limiting floorplans to those that have the slicing property can facilitate floorplanning algorithms.

- Taking the shape of a wheel floorplan and its mirror image as the basis of operators leads to hierarchical descriptions of order 5.

Unit 4 NTUEE / Intro. EDA 37

# B\*-Tree Perturbation • Op1: rotate a macro • Op2: delete & insert • Op3: swap 2 nodes • Op4: resize a soft macro Op3(n1, n7) Op2(n11, n6) Op3(n1, n6) Op3(n1, n7) Op3(n1, n6) Op3(n1, n7) Op3(n1, n6) Op3(n

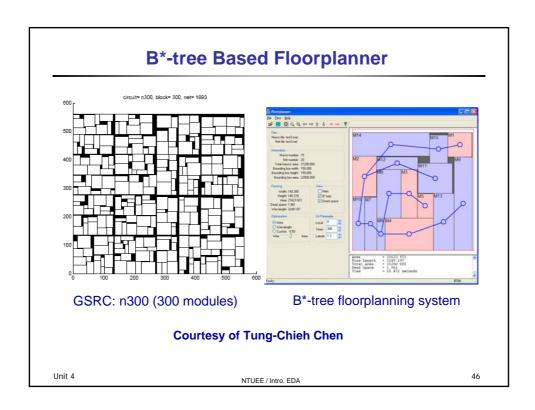

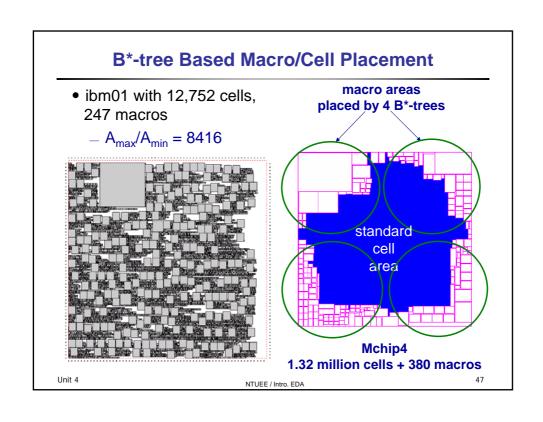

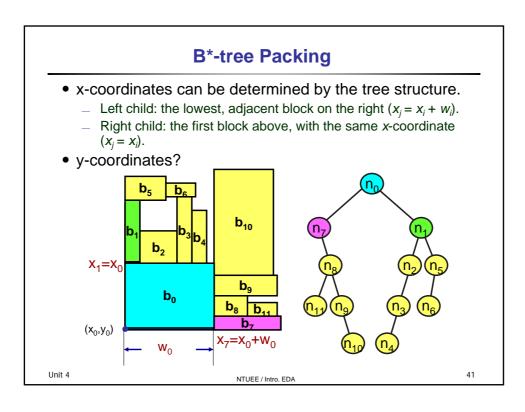

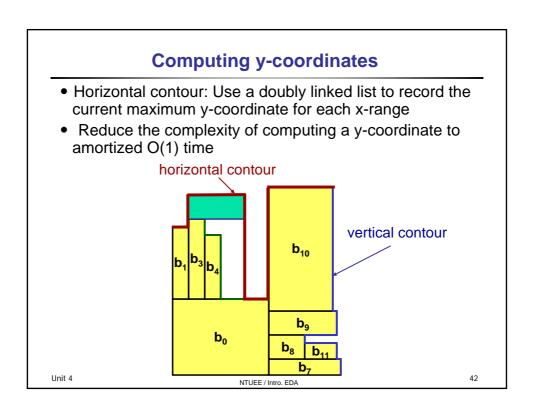

# **B\*-tree Floorplanning**

- Was considered as the best representation for packing in a recent survey (Chan et al., ISPD-05)

- More than 100 citations in ACM/IEEE papers since its publication at DAC-2K (> 70% of floorplanning papers)

- Package is available at http://eda.ee.ntu.edu.tw/research.htm/

| MCNC<br>Ckts | SP<br>(Japan)<br>1995 | Q-Seq<br>(Japan)<br>2002 | O-tree<br>(USA/<br>Japan)<br>1999 | CBL<br>(China)<br>2001 | Slicing<br>(USA)<br>2005 | TCG<br>(Ours)<br>DAC<br>2001 | TCG-S<br>(Ours)<br>DAC<br>2002 | CS<br>(Ours)<br>TVLSI<br>2003 | B*-tree<br>(Ours)<br>DAC<br>2000 |

|--------------|-----------------------|--------------------------|-----------------------------------|------------------------|--------------------------|------------------------------|--------------------------------|-------------------------------|----------------------------------|

| apte         | 48.12                 | 46.92                    | 47.1                              | NA                     | 46.92                    | 46.92                        | 46.92                          | 46.92                         | 46.92                            |

| xerox        | 20.69                 | 19.93                    | 20.1                              | 20.96                  | 20.20                    | 19.83                        | 19.796                         | 19.83                         | 19.796                           |

| hp           | 9.93                  | 9.03                     | 9.21                              | NA                     | 9.03                     | 8.947                        | 8.947                          | 8.947                         | 8.947                            |

| ami33        | 1.22                  | 1.194                    | 1.25                              | 1.20                   | 1.183                    | 1.20                         | 1.185                          | 1.18                          | 1.168                            |

| ami49        | 38.84                 | 36.75                    | 37.6                              | 38.58                  | 36.24                    | 36.77                        | 36.4                           | 36.24                         | 36.4                             |

Best chip areas are in red

Unit 4 NTUEE / Intro. EDA 45