#### **Unit 7: Detailed and Special Routing**

- Course contents

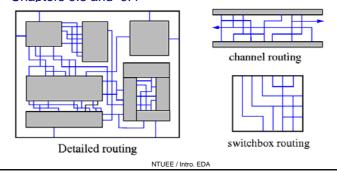

- Channel routing

- Full-chip routing

- Clock routing

- Power/ground routing

- Readings

Unit 7

Chapters 9.3 and 9.4

# **Routing Considerations**

- Number of terminals (two-terminal vs. multi-terminal nets)

- Net widths (power and ground vs. signal nets)

- Via restrictions (stacked vs. conventional vias)

- Boundary types (regular vs. irregular)

- Number of layers (two vs. three, more layers?)

- Net types (critical vs. non-critical nets)

Unit 7 NTUEF / Intro EDA 2

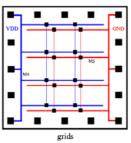

#### **Routing Models**

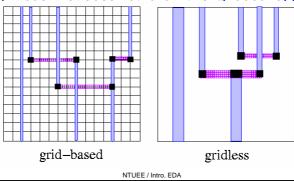

- Grid-based model:

- A grid is super-imposed on the routing region.

- Wires follow paths along the grid lines.

- Pitch: distance between two grid lines.

- Gridless model:

- Any model that does not follow this "gridded" approach.

Unit 7

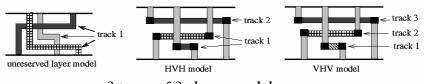

## **Models for Multi-Layer Routing**

- Unreserved layer model: Any net segment is allowed to be placed in any layer.

- Reserved layer model: Certain type of segments are restricted to particular layer(s).

- Two-layer: HV (horizontal-Vertical), VH

- \_ Three-layer: HVH, VHV

3 types of 3-layer models

Unit 7

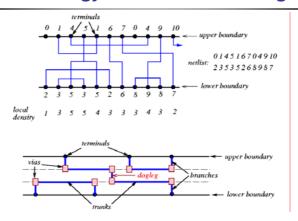

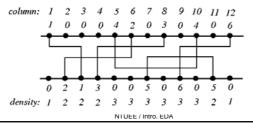

#### **Terminology for Channel Routing**

- Local density at column *i*, *d*(*i*): total # of nets that crosses column *i*.

- Channel density: maximum local density

- # of horizontal tracks required ≥ channel density.

Unit 7

NTUEE / Intro. EDA

5

# **Channel Routing Problem**

- Assignments of horizontal segments of nets to tracks.

- Assignments of vertical segments to connect.

- horizontal segments of the same net in different tracks, and

- the terminals of the net to horizontal segments of the net.

- Horizontal and vertical constraints must not be violated.

- Horizontal constraints between two nets: the horizontal span of two nets overlaps each other.

- Vertical constraints between two nets: there exists a column such that the terminal on top of the column belongs to one net and the terminal on bottom of the column belongs to another net.

- Objective: Channel height is minimized (i.e., channel area is minimized).

Unit 7

NTUEE / Intro. EDA

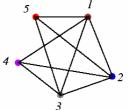

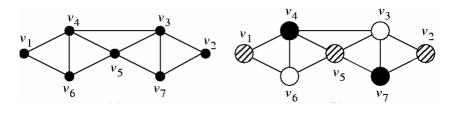

## **Horizontal Constraint Graph (HCG)**

- HCG G = (V, E) is **undirected** graph where

- $V = \{ v_i \mid v_i \text{ represents a net } n_i \}$

- $E = \{(v_i, v_j) | \text{ a horizontal constraint exists between } n_i \text{ and } n_j \}.$

- For graph G: vertices ⇔ nets; edge (i, j) ⇔ net i overlaps net j.

A routing problem and its HCG.

Unit 7

NTUEE / Intro. EDA

# **Vertical Constraint Graph (VCG)**

- VCG G = (V, E) is **directed** graph where

- $V = \{ v_i | v_i \text{ represents a net } n_i \}$

- $= E = \{(v_i, v_j) | \text{ a vertical constraint exists between } n_i \text{ and } n_j\}.$

- For graph G: vertices ⇔ nets; edge i → j ⇔ net i must be above net j.

A routing problem and its VCG.

Unit 7

NTUEE / Intro. ED

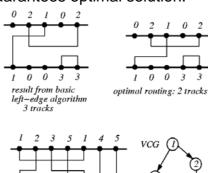

### 2-L Channel Routing: Basic Left-Edge Algorithm

- Hashimoto & Stevens, "Wire routing by optimizing channel assignment within large apertures," DAC-71.

- No vertical constraint.

- HV-layer model is used.

- Doglegs are not allowed.

- Treat each net as an interval.

- Intervals are sorted according to their left-end xcoordinates.

- Intervals (nets) are routed one-by-one according to the order.

- For a net, tracks are scanned from top to bottom, and the first track that can accommodate the net is assigned to the net.

- Optimality: produces a routing solution with the minimum # of tracks (if no vertical constraint).

Unit 7

NTUEE / Intro. EDA

9

## **Basic Left-Edge Algorithm**

```

Algorithm: Basic Left-Edge(U, track[i])

U: set of unassigned intervals (nets) I_1, ..., I_n;

I=[s_i, e_i]: interval j with left-end x-coordinate s_i and right-end e_i

track[j]: track to which net j is assigned.

1 begin

2 U \leftarrow \{I_1, I_2, ..., I_n\};

3 t \leftarrow 0;

4 while (U \neq \emptyset) do

5 t \leftarrow t + 1;

watermark \leftarrow 0;

7

while (there is an I_i \in U s.t. s_i > watermark) do

8

Pick the interval I_i \in U with s_i > watermark,

nearest watermark;

9

track[j] \leftarrow t

10

watermark \leftarrow e;

11

U \leftarrow U - \{I_i\};

12 end

Unit 7

```

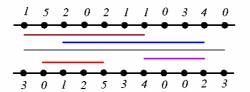

## **Basic Left-Edge Example**

- $U = \{I_1, I_2, ..., I_6\}$ ;  $I_1 = [1, 3]$ ,  $I_2 = [2, 6]$ ,  $I_3 = [4, 8]$ ,  $I_4 = [5, 10]$ ,  $I_5 = [7, 11]$ ,  $I_6 = [9, 12]$ .

- *t* =1:

- − Route  $I_1$ : watermark = 3;

- Route  $I_3$ : watermark = 8;

- Route  $I_6$ : watermark = 12;

- *t* = 2:

- Route  $l_2$ : watermark = 6;

- Route  $I_5$ : watermark = 11;

- t = 3: Route  $I_4$

Unit 7

11

# **Basic Left-Edge Algorithm**

- If there is no vertical constraint, the basic left-edge algorithm is optimal.

- If there is any vertical constraint, the algorithm no longer guarantees optimal solution.

Unit 7

## **Constrained Left-Edge Algorithm**

```

Algorithm: Constrained_Left-Edge(U, track[i])

U: set of unassigned intervals (nets) I_1, ..., I_n;

I = [s_i, e_i]: interval j with left-end x-coordinate s_i and right-end e_i

track[j]: track to which net j is assigned.

1 begin

2 U \leftarrow \{ I_1, I_2, ..., I_n \};

3 t \leftarrow 0;

4 while (U \neq \emptyset) do

t \leftarrow t + 1;

watermark \leftarrow 0;

while (there is an unconstrained I_i \in U s.t. s_i >

watermark) do

Pick the interval I_i \in U that is unconstrained,

with s_i > watermark, nearest watermark;

9

track[i] \leftarrow t

10

watermark \leftarrow e;

11

U \leftarrow U - \{I_i\};

12 end

NTUEE / Intro. EDA

```

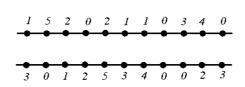

# **Constrained Left-Edge Example**

- $I_1 = [1, 3], I_2 = [1, 5], I_3 = [6, 8], I_4 = [10, 11], I_5 = [2, 6], I_6 = [7, 1]$

- Track 1: Route I<sub>1</sub> (cannot route I<sub>3</sub>); Route I<sub>6</sub>; Route I<sub>4</sub>.

- Track 2: Route  $l_2$ ; cannot route  $l_3$ .

- Track 3: Route  $I_5$ .

- Track 4: Route I<sub>3</sub>.

Unit 7

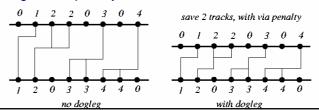

## **Dogleg Channel Router**

- Deutch, "A dogleg channel router," 13rd DAC, 1976.

- Drawback of Left-Edge: cannot handle the cases with constraint cycles.

- Doglegs are used to resolve constraint cycle.

- Drawback of Left-Edge: the entire net is on a single track.

- Doglegs are used to place parts of a net on different tracks to minimize channel height.

15

Might incur penalty for additional vias.

**Dogleg Channel Router**

- Each multi-terminal net is broken into a set of 2-terminal nets.

- Two parameters are used to control routing:

- Range: Determine the # of consecutive 2-terminal subnets of the same net that can be placed on the same track.

- Routing sequence: Specifies the starting position and the direction of routing along the channel.

- Modified Left-Edge Algorithm is applied to each subnet.

Unit 7 NTUFF / Intro FDA 1

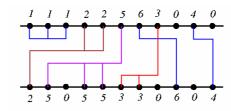

#### **Appendix: Robust Channel Router**

- Yoeli, "A robust channel router," IEEE TCAD, 1991.

- Alternates between top and bottom tracks until the center is reached.

- The working side is called the *current side*.

- Net weights are used to guide the assignment of segments in a track, which

- favor nets that contribute to the channel density;

- favor nets with terminals at the current side;

- penalize nets whose routing at the current side would cause vertical constraint violations.

- Allows unrestricted doglegs by rip-up and re-route.

Unit 7 NTUEE / Intro. EDA 17

#### **Robust Channel Router**

- Select the set of nets for the current side by solving the maximum weighted independent set problem for interval graphs.

- NP-complete for general graphs, but can be solved efficiently for interval graphs using dynamic programming.

- Main ideas:

- The interval for net *i* is denoted by  $[x_{i_{min}}, x_{i_{max}}]$ ; its weight is  $w_{i}$ .

- Process channel from left to right column; the optimal cost for position c is denoted by total[c];

- A net n with a rightmost terminal at position c is taken into the solution if total[c-1] <  $w_n$  + total[ $x_{n_{min}}-1$ ].

- Can apply maze routers to fix local congestion or to postprocess the results. (Why not apply maze routers to channel routing directly??)

Unit 7 NTUEF / Intro EDA 18

#### **Interval Graphs**

- There is a vertex for each interval.

- Vertices corresponding to overlapping intervals are connected by an edge.

- Solving the track assignment problem is equivalent to finding a **minimal vertex coloring** of the graph.

Unit 7 NTUEE / Intro. EDA 19

#### **Weight Computation**

- Computation of the weight w<sub>i</sub> for net i:

- favor nets that contribute to the channel density: add a large B

to w<sub>i</sub>.

- 2. favor nets with current side terminals at column x: add d(x) to  $w_i$ .

- 3. penalize nets whose routing at the current side would cause vertical constraint violations: subtract Kd(x) from  $w_i$ ,  $K = 5 \sim 10$ .

- Assume B = 1000 and K = 5 in the 1<sup>st</sup> iteration (top side):

- $\mathbf{w}_1 = (0) + (1) + (-5 * 2) = -9$

- Net 1 does not contribute to the channel density

- One net 1 terminal on the top

- Routing net 1 causes a vertical constraint from net 2 at column 2 whose density is 2

Unit 7

NTUEE / Intro. EDA

#### Weight Computation (cont'd)

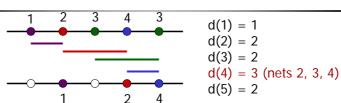

- d(1) = 1

- d(2) = 2

- d(3) = 2

- d(4) = 3 (nets 2, 3, 4)d(5) = 21 2 4

- Computation of the weight w<sub>i</sub> for net i:

- 1. favor nets that contribute to the channel density: add a large B to W<sub>i</sub>.

- 2. favor nets with current side terminals at column x: add d(x) to  $w_i$ .

- 3. penalize nets whose routing at the current side would cause vertical constraint violations: subtract Kd(x) from  $w_i$ ,  $K = 5 \sim 10$ .

- Assume B = 1000 and K = 5 in the 1<sup>st</sup> iteration (top side):

- $\mathbf{w}_1 = (0) + (1) + (-5 * 2) = -9$

- $\mathbf{w}_2 = (1000) + (2) + (-5 * 3) = 987$

- $w_3 = (1000) + (2+2) + (0) = 1004$

- $\mathbf{w}_4 = (1000) + (3) + (-5 * 2) = 993$

Unit 7

NTUEE / Intro. EDA

21

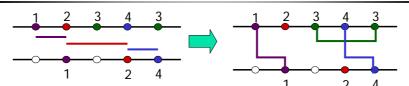

#### **Top-Row Net Selection**

- $W_1 = -9$ ,  $W_2 = 987$ ,  $W_3 = 1004$ ,  $W_4 = 993$ .

- A net *n* with a rightmost terminal at position *c* is taken into the solution if: total $[c-1] < w_n + \text{total}[x_{n_{min}} - 1]$ .

| total[1] = 0                              | selected_net[1] = 0 |

|-------------------------------------------|---------------------|

| total[2] = max(0, 0-9) = 0                | selected_net[2] = 0 |

| total[3] = 0                              | selected_net[3] = 0 |

| $total[4] = max(0, w_2 + total[1]) = 987$ | selected_net[4] = 2 |

| total[5] = max(987, 0+1004, 0+993) = 1004 | selected_net[5] = 3 |

Select nets backwards from right to left and with no horizontal constraints: Only net 3 is selected for the top row. (Net 2 is not selected since it overlaps with net 3.)

#### **Bottom-Row Net Selection**

- 2<sup>nd</sup> iteration: bottom-row selection

- $w_1 = (1000) + (2) + (0) = 1002$

- $w_2 = (1000) + (2) + (-5 * 2) = 992$

- $w_4 = (1000) + (1) + (-5 * 2) = 991$

| total[1] = 0                          | selected_net[1] = 0 |

|---------------------------------------|---------------------|

| total[2] = max(0, 0+1002) = 1002      | selected_net[2] = 1 |

| total[3] = 1002                       | selected_net[3] = 0 |

| total[4] = max(1002, 0+992) = 1002    | selected_net[4] = 0 |

| total[5] = max(1002, 1002+991) = 1993 | selected_net[5] = 4 |

• Nets 4 and 1 are selected for the bottom row.

Unit 7 NTUEE / Intro. EDA 23

#### Maze Routing + Rip-up & Re-route

- 3<sup>rd</sup> iteration

- Routing net 2 in the middle row leads to an infeasible solution.

- Apply maze routing and rip-up and re-route nets 2 and 4 to fix the solution.

Unit 7 NTLIEF / Intro. EDA 24

#### **Robust Channel Router** robust\_router (struct netlist N) set of int row; struct solution S; int total[channel\_width + 1], selected\_net[channel\_width $c \leftarrow \text{channel\_width}$ : int top, height, c, r, t; while (c > 0)if (selected\_net[c]) { height $\leftarrow$ density(N); for $(r \leftarrow 1; r \le \text{height}; r \leftarrow r + 1)$ { for all "nets i in netlist N" $n \leftarrow selected_net[c];$ $\mathsf{row} \leftarrow \mathsf{row} \, \mathsf{U} \, \{n\};$ $c \leftarrow x_{n_{min}} - 1;$ $w_i \leftarrow \text{compute\_weight}(N, \text{top});$ total[0] $\leftarrow$ 0; for $(c \leftarrow 1; c \le \text{channel.width}; c \leftarrow c + 1)$ { selected.net[c] $\leftarrow$ 0; $c \leftarrow c - 1$ ; solution ← solution U (row); selected $\operatorname{net}[c] \leftarrow 0$ , $\operatorname{total}[c] \leftarrow \operatorname{total}[c-1]$ ; if ("some net n has a top terminal at position c") if $(\mathbf{w}_n + \operatorname{total}[\mathbf{x}_{n_{min}} - 1]) > \operatorname{total}[c])$ { $\operatorname{total}[c] \leftarrow \mathbf{w}_n + \operatorname{total}[\mathbf{x}_{n_{min}} - 1]$ ; top ← !top; N ← "N without the nets selected in row" }/\* for \*/ "apply maze routing to eliminate possible vertical constraint violations" $\mathsf{selected} \, ... \mathsf{net}[c] \leftarrow n;$ $$\begin{split} &\text{if } (w_n + \text{total}[x_{n_{min}} - 1]) > \text{total}[c]) \\ &\text{total}[c] \leftarrow w_n + \text{total}[x_{n_{min}} - 1]); \\ &\text{selected.net}[c] \leftarrow n; \end{split}$$ )/\* if \*/ 25 Unit 7 NTUEE / Intro. EDA

## **Routing Trends**

- Billions of transistors may be fabricated in a single chip for nanometer technology.

- Need tools for very large-scale designs.

- Framework evolution for CAD tools

- Flat → Hierarchical → Multilevel

Pentium 4 42 M Transistors (Y2000)

Unit 7 NTUEF / Intro\_EDA 26

## **Flat Routing Framework**

- Sequential approaches

- Maze routing

- Concurrent approaches

- Network-flow based algorithms

- Drawback: hard to handle larger problems

Sequential

Concurrent

Unit 7

NTUEE / Intro. EDA

27

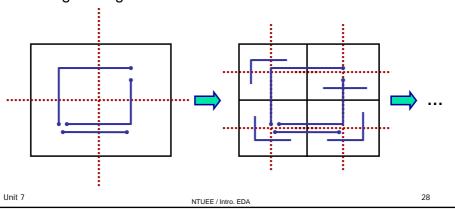

## **Hierarchical Routing Framework**

- The hierarchical approach recursively divides a routing region into a set of subregions and solve those subproblems independently.

- Drawbacks: lack the global information for the interaction among subregions.

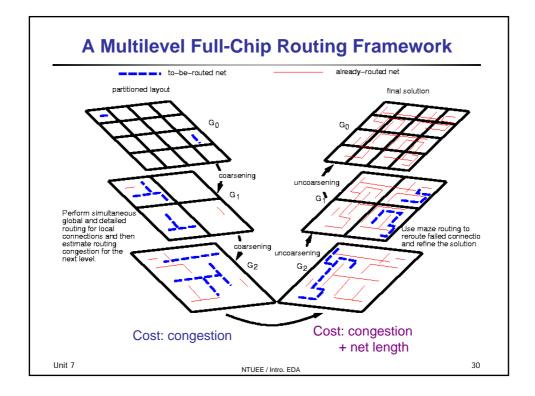

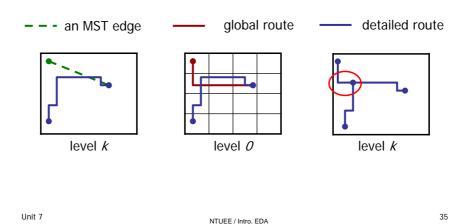

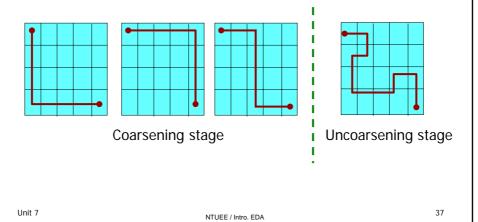

### **Multilevel Full-Chip Routing Framework**

- Lin and Chang, "A novel framework for multilevel routing considering routability and performance," ICCAD-2002 (TCAD, 2003).

- Multilevel framework: coarsening followed by uncoarsening.

- Coarsening (bottom-up) stage:

- Constructs the net topology based on the minimum spanning tree.

- Processes routing tiles one by one at each level, and only local nets (connections) are routed.

- Applies two-stage routing of global routing followed by detailed routing.

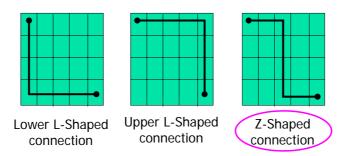

- Uses the L-shaped & Z-shaped pattern routing.

- Performs resource estimation after detailed routing to guide the routing at the next level.

- Uncoarsening (top-down) stage

- Completes the failed nets (connections) from the coarsening stage.

- Uses a global and a detailed maze routers to refine the solution.

Unit 7 NTUEE / Intro. EDA 29

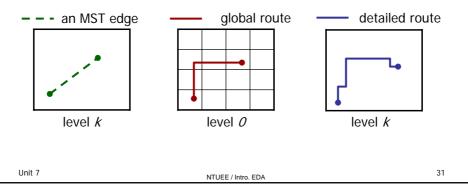

### **Coarsening Stage**

- Build MSTs for all nets and decompose them into twopin connections.

- Route local nets (connections) from level 0.

- Two-stage routing (global + detailed routing) for a local net.

### **Global Routing**

- Apply pattern routing for global routing

- Use L-shaped and Z-shaped connections to route nets.

- Has lower time complexity than maze routing.

Unit 7 NTLIEF / Intro. EDA 32

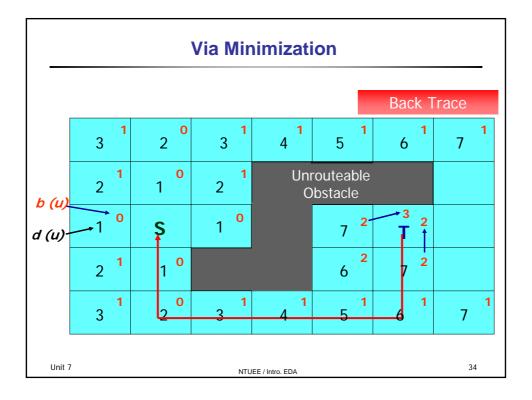

# **Detailed Routing**

- Via minimization

- Modify the maze router to minimize the number of bends.

- Local refinement

- Apply general maze routing to improve the detailed routing results.

- Resource estimation

- Update the edge weights of the routing graph after detailed routing.

Unit 7 NTUEE / Intro. EDA 33

#### **Local Refinement**

Local refinement improves detailed routing results by merging two connections which are decomposed from the same net.

#### **Resource Estimation**

- Global routing cost is the summation of congestions of all routed edges.

- Define the congestion, C<sub>e</sub>, of an edge e by

$$C_e = \frac{1}{2^{(p_e - d_e)}},$$

where  $p_{\rm e}$  and  $d_{\rm e}$  are the capacity and density, respectively.

• Update the congestion of routed edges to guide the subsequent global routing.

Unit 7 NTUEF / Intro EDA 36

### **Uncoarsening Global Routing**

- Use maze routing.

- Iterative refinement of a failed net is stop when a route is found or several tries have been made.

# **Routing Comparisons**

- 100% routing completion for all (11) benchmark circuits

- Three-level routing: 0 completion (ISPD-2K)

- Hierarchical routing: 2 completions (ICCAD-2001)

- Previous multilevel routing: 2 completions (ICCAD-2001)

- Can complete routings using even fewer routing layers.

| Ex.    | #Layers | (A) Three-Level Routing |       | el Routing (B) Hierarchical Routing<br>with Ripup and Replan |         | (C) Results of [9] |       |         | (D) Our Results |       |         |       |       |

|--------|---------|-------------------------|-------|--------------------------------------------------------------|---------|--------------------|-------|---------|-----------------|-------|---------|-------|-------|

|        |         | Time(s)                 | #Rtd. | Cmp.                                                         | Time(s) | #Rtd.              | Cmp.  | Time(s) | #Rtd.           | Cmp.  | Time(s) | #Rtd. | Cmp.  |

|        |         |                         | Nets  | Rates                                                        |         | Nets               | Rates |         | Nets            | Rates |         | Nets  | Rates |

| Mcc1   | 4       | 933.2                   | 1499  | 88%                                                          | 947.9   | 1600               | 94.5% | 436.7   | 1683            | 99.4% | 204.7   | 1694  | 100%  |

| Mcc2   | 4       | 12333.6                 | 5451  | 72.3%                                                        | 10101.4 | 7161               | 95.6% | 7644.8  | 7474            | 99.1% | 7203.3  | 7541  | 100%  |

| Struct | 3       | 406.2                   | 3530  | 99.4%                                                        | 324.5   | 3551               | 100%  | 316.8   | 3551            | 100%  | 151.5   | 3551  | 100%  |

| Prim1  | 3       | 239.1                   | 2018  | 99.0%                                                        | 353.0   | 2037               | 100%  | 350.2   | 2037            | 100%  | 165.4   | 2037  | 100%  |

| Prim2  | 3       | 1331                    | 8109  | 98.9%                                                        | 2423.8  | 8194               | 100%  | 2488.4  | 8196            | 100%  | 788.2   | 8197  | 100%  |

| S5378  | 3       | 430.2                   | 2607  | 83.4%                                                        | 57.9    | 2964               | 94.9% | 54.0    | 2963            | 94.8% | 10.9    | 3124  | 100%  |

| S9234  | 3       | 355.2                   | 2467  | 88.9%                                                        | 40.7    | 2564               | 92.4% | 41.0    | 2561            | 92.3% | 7.7     | 2774  | 100%  |

| S13207 | 3       | 1099.5                  | 6118  | 87.5%                                                        | 161.9   | 6540               | 93.5% | 188.8   | 6574            | 94.0% | 38.2    | 6995  | 100%  |

| S15850 | 3       | 1469.1                  | 7343  | 88.2%                                                        | 426.1   | 7874               | 94.6% | 403.4   | 7863            | 94.5% | 57.5    | 8321  | 100%  |

| s38417 | 3       | 3560.9                  | 19090 | 90.8%                                                        | 754.6   | 19596              | 93.2% | 733.6   | 19636           | 93.3% | 137.6   | 21035 | 100%  |

| S38584 | 3       | 7086.5                  | 25642 | 91.0%                                                        | 1720    | 26461              | 93.9% | 1721.6  | 26504           | 94.1% |         | 28177 | 100%  |

| avg.   |         |                         |       | 89.8%                                                        |         |                    | 95.7% |         |                 | 96.5% |         |       | 100%  |

Table 3: Comparison among (A) the three-level routing [10], (B) the hierarchical routing [9], (C) the multilevel routing [9], and (D) our multilevel routing. Note: (A),(B),(C) ran on a 440 Mhz Sun Ultra-5 with 384 MB memory, (D) ran on a 450Mhz Sun Spare Ultra-60 with 2GB MB.

Unit 7 NTUEE / Intro. EDA 38

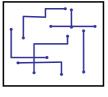

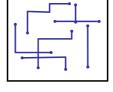

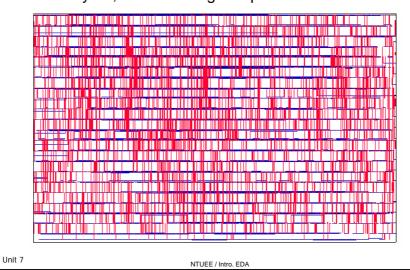

## **Routing Solution for Prim2**

- 0.18um technology, pitch = 1 um, 8109 nets.

- Two layers, 100% routing completion.

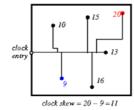

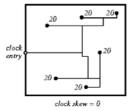

# **The Clock Routing Problem (CRP)**

- Digital systems

- Synchronous systems: Highly precised clock achieves communication and timing.

- Asynchronous systems: Handshake protocol achieves the timing requirements of the system.

- Clock skew is defined as the difference in the minimum and the maximum arrival time of the clock.

- . CRP: Routing clock nets such that

- 1. clock signals arrive simultaneously

- 2. clock delay is minimized

- Other issues: total wirelength, power consumption, etc

Unit 7

NTUEE / Intro. EDA

40

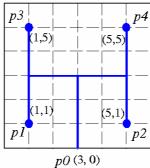

#### **Clock Routing Problem**

- Given the routing plane and a set of points P = {p<sub>1</sub>, p<sub>2</sub>, ..., p<sub>n</sub>} within the plane and clock entry point p<sub>0</sub> on the boundary of the plane, the Clock Routing Problem (CRP) is to interconnect each p<sub>i</sub> ∈ P such that max<sub>i, j ∈ P</sub>|t(0, i) t(0, j)| and max<sub>i ∈ P</sub> t(0, i) are both minimized.

- Pathlength-based approaches

- H-tree: Dhar, Franklin, Wang, ICCD-84; Fisher & Kung, 1982.

- RC-delay based approaches:

- Exact zero skew: Tsay, ICCAD-91.

Unit 7 NTUEE / Intro. EDA

## **H-Tree Based Algorithm**

• *H*-tree: Dhar, Franklin, Wang, "Reduction of clock delays in VLSI structure," ICCD-84.

H-tree over 4 points

H-tree over 16 points

41

Unit 7 NTUEF / Intro EDA 42

## **Elmore Delay: Nonlinear Delay Model**

- Parasitic resistance and capacitance dominate delay in deep submicron wires.

- Resistor  $r_i$  must charge all downstream capacitors.

- Elmore delay: Delay can be approximated as sum of sections: resistance × downstream capacitance.

$$\delta = \sum_{i=1}^{n} \left( r_{i} \sum_{k=i}^{n} c_{k} \right) = \sum_{i=1}^{n} r(n-i+1)c = \frac{n(n+1)}{2}rc.$$

$$V_{\text{in}} \quad C_{1} \quad C_{2} \quad C_{3} \quad \cdots \quad V_{\text{out}}$$

• Delay grows as **square** of wire length.

Unit 7

NTUEE / Intro. ED/

43

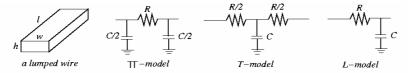

#### **Wire Models**

Lumped circuit approximations for distributed RC lines: π-model (most popular), T-model, L-model.

•  $\pi$ -model: If no capacitive loads for C and D,

A to B:

$$\delta_{AB} = r_1 (c_1/2 + c_2 + c_3);$$

B to C:  $\delta_{BC} = r_2 (c_2/2);$

B to D:  $\delta_{BD} = r_3 (c_3/2).$

Unit 7

NTUEE / Intro. EDA

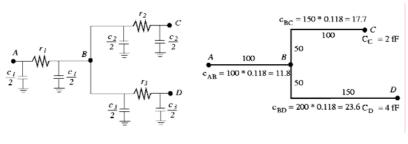

## **Example Elmore Delay Computation**

- 0.18  $\mu m$  technology.: unit resistance  $\hat{r} = 0.075 \ \Omega / \mu m$ ; unit capacitance  $\hat{c} = 0.118 \ fF/\mu m$ .

- Assume  $C_C = 2$  fF,  $C_D = 4$  fF.

- $\delta_{BC} = r_{BC} (c_{BC}/2 + C_C) = 0.075 \times 150 (17.7/2 + 2) = 120 \text{ fs}$

- $\delta_{BD} = r_{BD} (c_{BD}/2 + C_D) = 0.075 \times 200 (23.6/2 + 4) = 240 \text{ fs}$

- $-\delta_{AB} = r_{AB} (c_{AB}/2 + C_B) = 0.075$  × 100 (11.8/2 + 17.7 + 2 + 23.6 + 4) = 400 fs

- Critical path delay:  $\delta_{AB} + \delta_{BD} = 640$  fs.

Unit 7

NTUEE / Intro. EDA

45

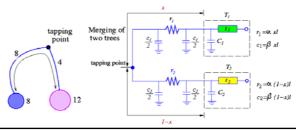

## **Exact Zero Skew Algorithm**

- Tsay, "Exact zero skew algorithm," ICCAD-91.

- To ensure the delay from the tapping point to leaf nodes of subtrees T<sub>1</sub> and T<sub>2</sub> being equal, it requires that

$$r_1 (c_1/2 + C_1) + t_1 = r_2 (c_2/2 + C_2) + t_2.$$

• Solving the above equation, we have

$$x = \frac{(t_2 - t_1) + \alpha l \left(C_2 + \frac{\beta l}{2}\right)}{\alpha l (\beta l + C_1 + C_2)}$$

where  $\alpha$  and  $\beta$  are the per unit values of resistance and capacitance, *I* the length of the interconnecting wire,  $r_1 = \alpha xI$ ,  $c_1 = \beta xI$ ,  $r_2 = \alpha(1 - x) I$ ,  $c_2 = \beta(1 - x)I$ .

Unit 7

### **Zero-Skew Computation**

- Balance delays:  $r_1(c_1/2 + C_1) + t_1 = r_2(c_2/2 + C_2) + t_2$ . Compute tapping points  $x = \frac{(t_2 t_1) + \alpha l \left(C_2 + \frac{\beta l}{2}\right)}{\alpha l (\beta l + C_1 + C_2)}$ ,  $\chi(\beta)$ : per unit values of resistance (capacitance); *I*: length of the wire;

$$r_1 = \alpha \ xI, \ c_1 = \beta x \ I; \ r_2 = \alpha (1 - x) \ I, \ c_2 = \beta (1 - x) \ I.$$

- If  $x \notin [0, 1]$ , we need **snaking** to find the tapping point.

- Exp:  $\alpha = 0.1 \Omega$  /unit,  $\beta = 0.2 F$ /unit. (Find tapping points E for A and B, F for C and D, and G for E and F.)

47

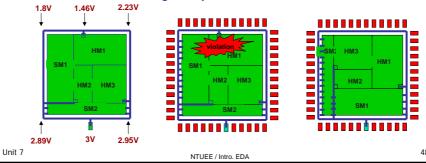

# IR (Voltage) Drop

- Power consumption and rail parasitics cause actual supply voltage to be lower than ideal

- Metal width tends to decrease with length increasing in nanometer design

- Effects of IR drop

Unit 7

- Reducing voltage supply reduces circuit speed (5% IR drop => 15% delay increase)

- Reduced noise margin may cause functional failures

# Power/Ground (P/G) Routing

- Are usually laid out entirely on metal layers for smaller parasitics.

- Two steps:

- 1. **Construction of interconnection topology:** non-crossing power, ground trees.

- 2. Determination of wire widths: prevent metal migration, keep voltage (IR) drop small, widen wires for more powerconsuming modules and higher density current (1.5 mA per μ m width for Al). (So area metric?)

Unit 7