# Computer-Aided VLSI System Design, Fall 2011 Verilog Lab 1: 4-Bit ALU with 2 Instructions

I. 4-Bit ALU with 2 Instructions:

#### II. Objectives:

In this lab, you will learn:

- 1. A synthesizable Verilog HDL code and the corresponding test bench.

- 2. How to run NC-Verilog simulator?

#### III. Environment Setup:

Source the default *cshrc* file: source /usr/cadence/cshrc

### IV. Lab Files:

- 1. Lab files are in ~cvsd/11F/Verilog/Lab1.tar

- Extract Labl.tar in your working directory with command tar -xvf Labl.tar

- 3. Lab1 files are shown as below:

| Filename             | Description              |

|----------------------|--------------------------|

| Lab1_alu.v           | RTL code for this ALU    |

| Lab1_test_alu.v      | Test bench for this ALU  |

| Lab1_alu_run.f       | Command-line file        |

| Lab1_test_alu_file.v | Test bench with file I/O |

| program.txt          | Input stimulus           |

| program_out.txt      | Correct answers          |

#### NTUEE GIEE

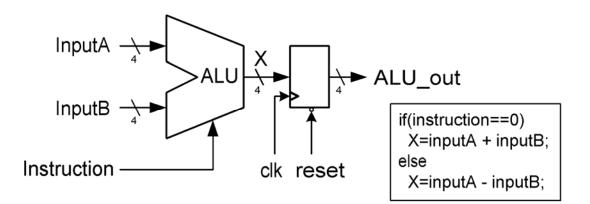

4. Your ALU module looks like this

```

module ALU(alu_out,instruction,inputA,inputB,clk,reset);

output [3:0] alu_out;

input [3:0] inputA,inputB;

input instruction;

input clk,reset;

```

...

endmodule

#### V. Module Description:

This RTL describes a simple ALU with two 4-bit input signals and 2 instructions. One instruction is summation, and the other one is subtraction.

### VI. Check Verilog Code by NC-Verilog:

1. Type this command

ncverilog Lab1\_alu.v

- 2. NC-Verilog will report one error because the signal X is not declared. **Please** help to add the declaration for the file *Lab1\_alu.v*.

- 3. Run the command in step 1 again. No error should occur now.

#### VII. Run simulation with a test bench by NC-Verilog:

1. Type this command

ncverilog Lab1\_test\_alu.v Lab1\_alu.v

- 2. 224 errors are found after simulation. Please read the file *alu\_out.txt* to find out what happens. **Please modify the file** *Lab1\_alu.v* to fix these errors.

- 3. Run the command in step 1 again. The simulation result is correct now.

- 4. Instead of the command in step 1, you can also use the command-line file to run simulation by typing this command.

```

ncverilog -f Lab1_alu_run.f

```

# VIII. Run simulation with file I/O:

1. Using the test bench *Lab1\_test\_alu\_file.v* for simulation. Can you find out how this test bench works with file I/O?

\$readmemb("program.txt",program); // Input stimulus

\$readmemb("program\_out.txt",answer); // Correct answers

# IX. Checkpoints:

Please check with TAs before leaving this lab to make sure the following goals are accomplished and to get credits.

- 1. Please fix the declaration error in Section VI.

- 2. Please fix the simulation errors in Section VII.

## END of LAB

### **Creator:**

- 1<sup>st</sup> Edition: Chao-Tsung Huang, 2002

- 2<sup>nd</sup> Edition: Yu-Lin Chang, 2004

- 3<sup>rd</sup> Edition: Yu-Lin Chang, 2005

- 4<sup>th</sup> Edition: En-Jui Chang, 2010

- 5<sup>th</sup> Edition: En-Jui Chang, 2011