# Switching Circuits & Logic Design

Jie-Hong Roland Jiang 江介宏

Department of Electrical Engineering National Taiwan University

Fall 2012

1

## §13 Analysis of Clocked Sequential Circuits

Magic Mirror M.C. Escher, 1946

### Outline

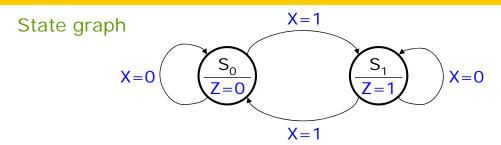

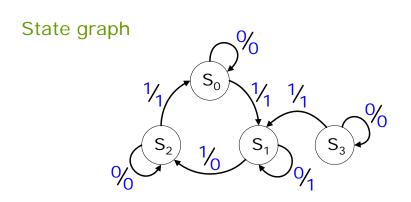

- ■A sequential parity checker

- Analysis by signal tracing and timing charts

- ■State tables and graphs

- General models for sequential circuits

3

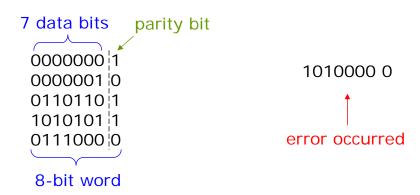

## A Sequential Parity Checker

- When binary data is transmitted or stored, an extra bit (call a parity bit) is frequently added for the purposes of error detection

- Odd (even) parity: the total number of 1's in the block, including the parity bit, is odd (even)

Example (8-bit words with odd parity)

## A Sequential Parity Checker

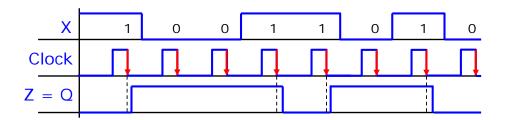

- A parity checker for serial data

- Z = 1 ⇔ the total number of 1 inputs received is odd (i.e., input parity is odd)

- $\blacksquare$  Z = 0 initially

Clock

Block diagram

5

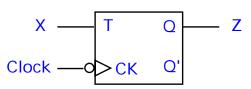

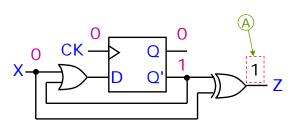

## A Sequential Parity Checker

#### State table

|                | Next State<br>X=0 X=1         | Present<br>Output |   | Q | X=0 | ! <sup>+</sup><br>X=1 | X=0 | Г<br>Х=1 | Z |

|----------------|-------------------------------|-------------------|---|---|-----|-----------------------|-----|----------|---|

| S <sub>0</sub> | S <sub>0</sub> S <sub>1</sub> | 0                 | _ | 0 | 0   | 1                     | 0   | 1        | 0 |

| $S_1$          | $S_1 S_0$                     | 1                 |   | 1 | 1   | 0                     | 0   | 1        | 1 |

#### Logic circuit

6

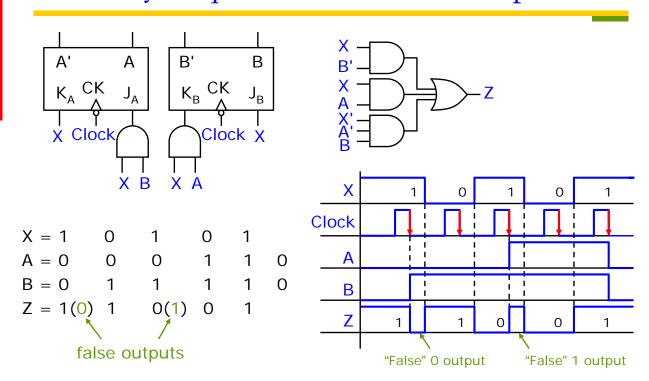

## Signal Tracing and Timing Charts

- Find the output sequence resulting from a given input sequence by tracing 0 and 1 signals through a circuit

- 1. Assume an initial state of the flip-flops

- 2. Given a current input at the present state, determine the circuit outputs and next state (flip-flop inputs)

- 3. Update the present state to the next state, and repeat 2

A sequential circuit with n FFs has 2<sup>n</sup> states

7

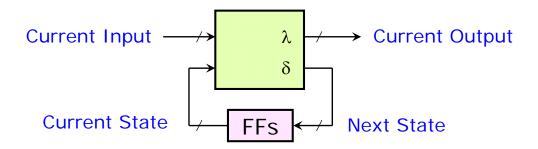

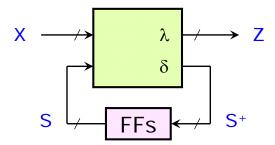

## Signal Tracing and Timing Charts

- There are two types of clocked sequential circuits

- Moore machine

- Output depends only on the present state

- Output function  $\lambda(S)$

- Mealy machine

- Output depends on both the present state and the input

- Output function  $\lambda(S,X)$

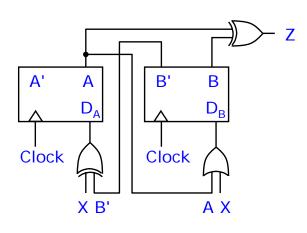

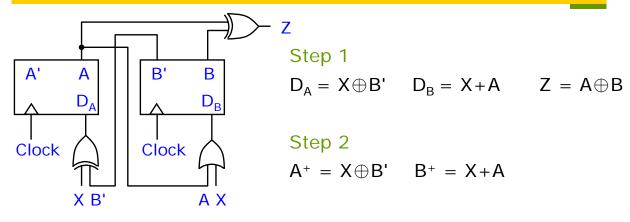

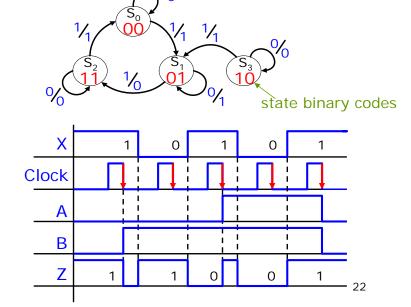

## Signal Tracing and Timing Charts A Moore Sequential Circuit Example

#### Assume A=B=0 initially

$$X = 0 \quad 1 \quad 1 \quad 0 \quad 1$$

$A = 0 \quad 1 \quad 0 \quad 1 \quad 0 \quad 1$

$B = 0 \quad 0 \quad 1 \quad 1 \quad 1 \quad 1$

$Z = (0) \quad 1 \quad 1 \quad 0 \quad 1 \quad 0$

Output is a function of states only ⇒ a Moore circuit

9

## Signal Tracing and Timing Charts Moore Sequential Circuit

- □ For a Moore circuit, the output which results from application of a given input does not appear until after the active clock edge

- The output sequence is displaced in time with respect to the input sequence

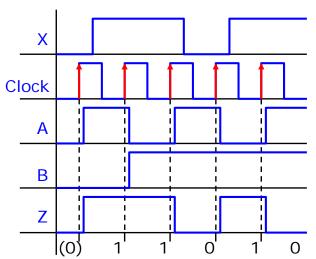

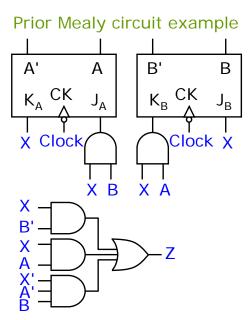

## Signal Tracing and Timing Charts A Mealy Sequential Circuit Example

Output is a function of both states and inputs  $\Rightarrow$  a Mealy circuit

## Signal Tracing and Timing Charts Mealy Sequential Circuit

- ☐ For a Mealy circuit, the output may temporarily assume an incorrect value (called a **false output**, **glitch**, **spike**)

- The false output occurs after the circuit has changed state and before the input is changed; however, the correct output must appear before the active clock edge

- □ No false output can appear in a Moore circuit

- The output sequence is not displaced in time with respect to the input sequence

- If the output of the circuit is fed into a second sequential circuit which uses the same clock, the false outputs will not cause any problem because the inputs to the second circuit can cause a change of state only at the active clock edge

12

## State Tables and Graphs

- Procedure to construct the state table

- Determine the FF input equations and output equations from the circuit

- Derive the next-state equation for each FF from its input equations

- D FF Q+ = [

- D-CE FF  $Q^+ = D \cdot CE + Q \cdot CE'$

- $\blacksquare$  T FF  $Q^+ = T \oplus Q$

- $\blacksquare$  S-R FF  $Q^+ = S + R'Q$

- 3. Plot a next-state map for each FF

- Combine these maps to form the state table (or called transition table)

13

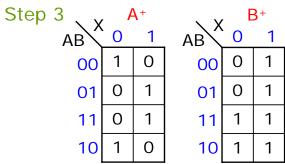

## State Tables and Graphs A Moore Sequential Circuit Example

Step 4

|    | A+  |     |   |

|----|-----|-----|---|

| AB | X=0 | X=1 | Z |

| 00 | 10  | 01  | 0 |

| 01 | 00  | 11  | 1 |

| 11 | 01  | 11  | 0 |

| 10 | 11  | 01  | 1 |

14

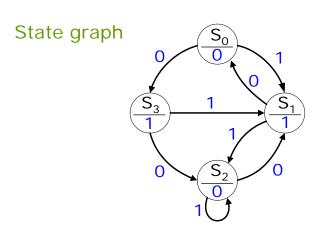

## State Tables and Graphs A Moore Sequential Circuit Example

#### State tables

|    | A+  | B <sup>+</sup> |   |                                             | Present        | Next  | State          | Present    |

|----|-----|----------------|---|---------------------------------------------|----------------|-------|----------------|------------|

| AB | X=0 | X=1            | Z | - Cymabalia                                 | State          | X=0   | X=1            | Output (Z) |

| 00 | 10  | 01             | 0 | <ul> <li>Symbolic representation</li> </ul> | S <sub>0</sub> | $S_3$ | S <sub>1</sub> | 0          |

| 01 | 00  | 11             | 1 | representation                              | $S_1$          | $S_0$ | $S_2^{\cdot}$  | 1          |

| 11 | 01  | 11             | 0 |                                             | $S_2$          | $S_1$ | $S_2$          | 0          |

| 10 | 11  | 01             | 1 |                                             | $S_3$          | $S_2$ | $S_1$          | 1          |

15

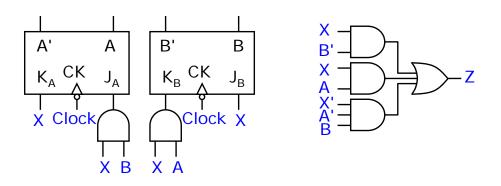

## State Tables and Graphs A Mealy Sequential Circuit Example

#### Steps 1,2

$$A^{+} = J_{A}A' + K'_{A}A = XBA' + X'A$$

$B^{+} = J_{B}B' + K'_{B}B = XB' + (AX)'B = XB' + X'B + A'B$

$$Z = X'A'B + XB' + XA$$

## State Tables and Graphs A Mealy Sequential Circuit Example

#### Step 3

| ABX | 0  | 1 | ABX | 0 | 1 | ABX | 0 | 1 |

|-----|----|---|-----|---|---|-----|---|---|

| 00  | 0  | 0 | 00  | 0 | 1 | 00  | 0 | 1 |

| 01  | 0  | 1 | 01  | 1 | 1 | 01  | 1 | 0 |

| 11  | 1  | 0 | 11  | 1 | 0 | 11  | 0 | 1 |

| 10  | 1  | 0 | 10  | 0 | 1 | 10  | 0 | 1 |

| ·   | A+ |   |     | В | + |     | Z | 7 |

#### Step 4

|    | A+  | B+  |     | <u>7</u> |

|----|-----|-----|-----|----------|

| AB | X=0 | X=1 | X=0 | X=1      |

| 00 | 00  | 01  | 0   | 1        |

| 01 | 01  | 11  | 1   | 0        |

| 11 | 11  | 00  | 0   | 1        |

| 10 | 10  | 01  | 0   | 1        |

17

## State Tables and Graphs A Mealy Sequential Circuit Example

#### State tables

| AB | A+<br>X=0 | -B+ | X=0 | <u>7</u><br>X=1 |                         | Present<br>State | Next<br>X=0    | State<br>X=1   | l | sent<br>tput<br>X=1 |

|----|-----------|-----|-----|-----------------|-------------------------|------------------|----------------|----------------|---|---------------------|

| 00 | 00        | 01  | 0   | 1               | Symbolic representation | S <sub>0</sub>   | S <sub>0</sub> | S <sub>1</sub> | 0 | 1                   |

| 01 | 01        | 11  | 1   | 0               | representation          | $S_1$            | $S_1$          | $S_2$          | 1 | 0                   |

| 11 | 11        | 00  | 0   | 1               |                         | $S_2$            | $S_2$          | $S_0$          | 0 | 1                   |

| 10 | 10        | 01  | 0   | 1               |                         | $S_3$            | $S_3$          | $S_1$          | 0 | 1                   |

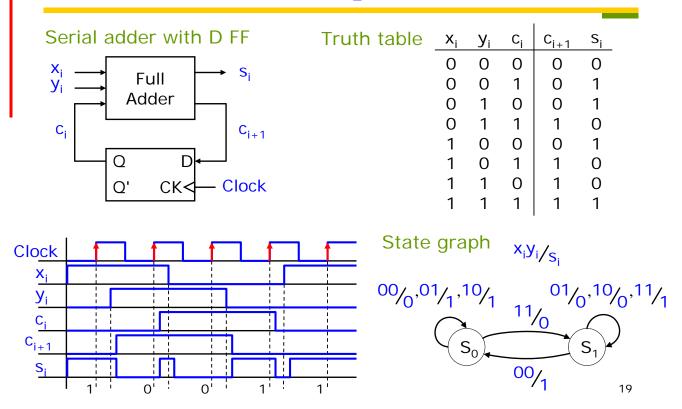

## State Tables and Graphs A Serial Adder Example

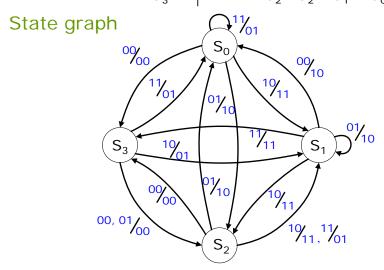

## State Tables and Graphs Example w/ Multiple Inputs & Outputs

| State table | Present          | Next State    |       |                |                | Present O     | utput | (Z <sub>1</sub> Z | <u>7</u> <sub>2</sub> ) |

|-------------|------------------|---------------|-------|----------------|----------------|---------------|-------|-------------------|-------------------------|

|             | State            | $X_1X_2 = 00$ | 01    | 10             | 11             | $X_1X_2 = 00$ | 01    | 10                | 11                      |

|             | $\overline{S_0}$ | $S_3$         | $S_2$ | S <sub>1</sub> | S <sub>0</sub> | 00            | 10    | 11                | 01                      |

|             | $S_1$            |               | $S_1$ | -              | $S_3$          | 10            | 10    | 11                | 11                      |

|             | $S_2$            | $S_3$         | $S_0$ | $S_1^-$        | $S_1$          | 00            | 10    | 11                | 01                      |

|             | $S_3^-$          | $S_2$         | $S_2$ | S₁ .           | $S_0$          | 00            | 00    | 01                | 01                      |

Given an initial state and an input sequence, we know the corresponding state trace and output sequence

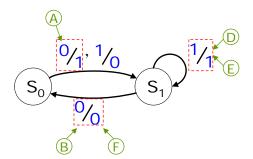

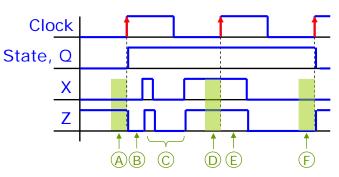

## State Tables and Graphs Timing Charts

Construction and interpretation of timing charts

| Q |                                  | Present<br>X=0 | State<br>X=1 | X=0      | X = 1       |

|---|----------------------------------|----------------|--------------|----------|-------------|

| 0 | S <sub>0</sub><br>S <sub>1</sub> | S1<br>S0       | S1<br>S1     | 0<br>B F | 0<br>1<br>E |

Initial values are shown

Read X and Z in shaded area

#### 21

## State Tables and Graphs Signal Tracing and Timing Charts

☐ To plot a timing chart for a sequential circuit, the state graph (with states encoded in binary codes) can be a better reference than the circuit itself

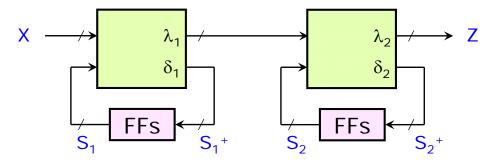

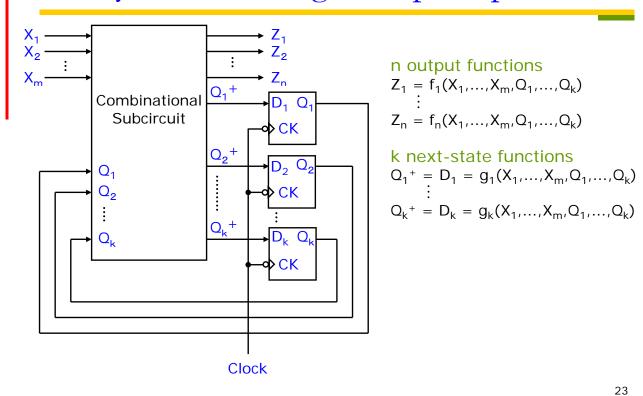

## General Models for Sequential Circuits Mealy Circuit Using D Flip-Flops

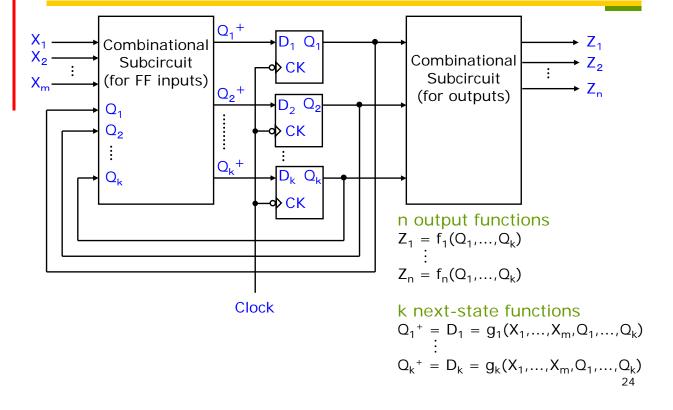

## General Models for Sequential Circuits Moore Circuit Using D Flip-Flops

## General Models for Sequential Circuits Unary Representation

Example (prior example with multiple inputs and outputs)

| Present | Nex   | kt Sta  | ate            | Present        | Outp  | out (Z | () |   |

|---------|-------|---------|----------------|----------------|-------|--------|----|---|

| State   | X = 0 | 1       | 2              | 3              | X = 0 | 1      | 2  | 3 |

| $S_0$   | $S_3$ | $S_2$   | S <sub>1</sub> | S <sub>0</sub> | 0     | 2      | 3  | 1 |

| $S_1$   | $S_0$ | $S_1^-$ | $S_2$          | $S_3$          | 2     | 2      | 3  | 3 |

| $S_2$   | $S_3$ | $S_0$   | $S_1^-$        | $S_1$          | 0     | 2      | 3  | 1 |

| $S_3^-$ | $S_2$ | $S_2$   | $S_1$          | $S_0$          | 0     | 0      | 1  | 1 |

25

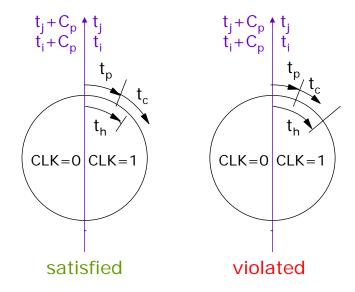

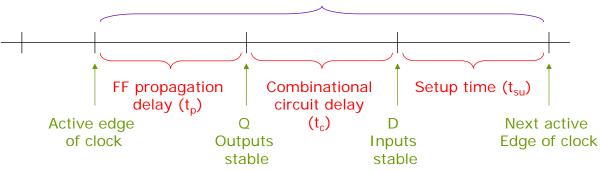

### General Models for Sequential Circuits Minimum Clock Period

- The minimum clock period

- $t_{clk}(min) = t_x + t_c + t_{su}$ , where  $t_x$  is the time after the active clock edge at which the X inputs are stable

- $\blacksquare$   $t_{clk}(min) = t_p + t_c + t_{su'}$  if  $t_x \le t_p$

Minimum clock period ( $t_{clk}$ )

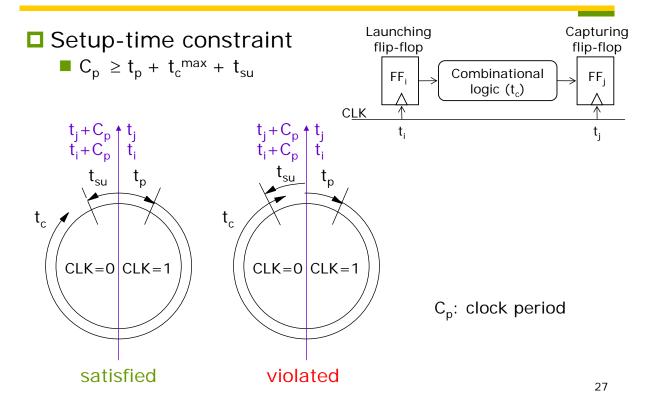

## General Models for Sequential Circuits Timing Constraints

## General Models for Sequential Circuits Timing Constraints

- Hold-time constraint

- $\blacksquare$   $t_p + t_c^{min} \ge t_h$