#### Introduction to Logic Synthesis with ABC

#### Alan Mishchenko

UC Berkeley

#### Overview

- (1) Problems in logic synthesis

Representations and computations

(2) And-Inverter Graphs (AIGs)

The foundation of innovative synthesis

(3) AIG-based solutions

Synthesis, mapping, verification

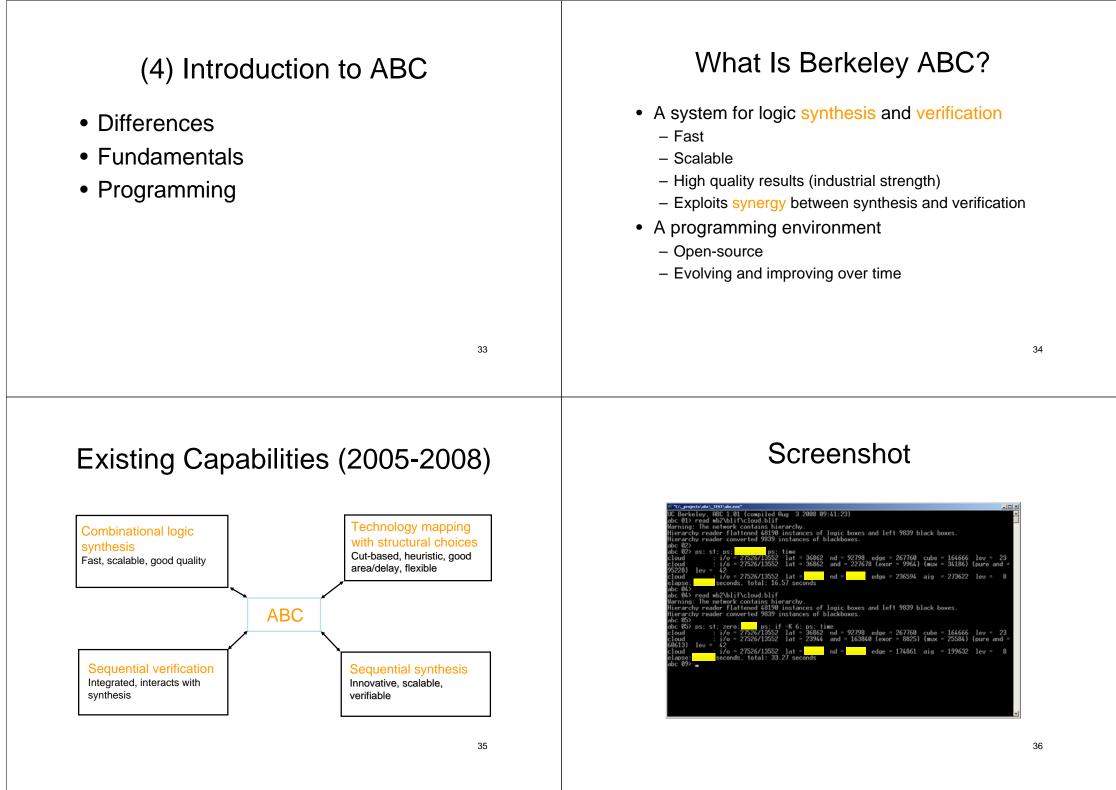

(4) Introduction to ABC

Differences, fundamentals, programming

- (5) Programming assignment

# (1) Problems in Synthesis

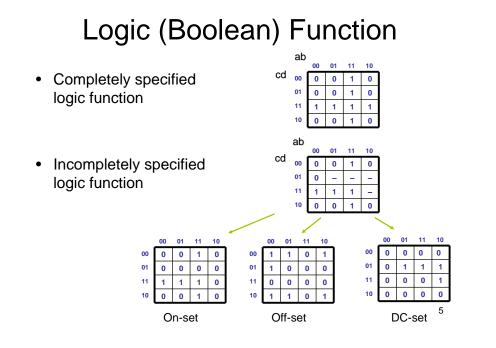

- What are the objects to be "synthesized"?

- Logic structures

- Boolean functions (with or without don't-cares)

- State machines, relations, sets, etc.

- How to represent them efficiently?

- Depends on the task to be solved

- Depends on the size of an object

- How to create, transform, minimize the representations?

- Multi-level logic synthesis

- Technology mapping

- How to verify the correctness of the design?

- Gate-level equivalence checking

- Property checking

- Etc.

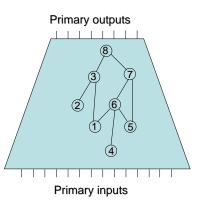

# Terminology

- Logic function (e.g. F = ab+cd)

- Variables (e.g. b)

- Minterms (e.g. abcd)

- Cube (e.g. ab)

- Logic network

- Primary inputs/outputs

- Logic nodes

- Fanins/fanouts

- Transitive fanin/fanout cone

- Cut and window (defined later)

TFI Primary inputs

Primary outputs

1 1 1

TFO /

● Fanouts

b, Fanins

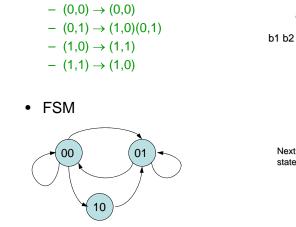

#### Relations

• Relation  $(a1,a2) \rightarrow (b1,b2)$

Characteristic function

0

a1 a2

11

**Representation Zoo**

Find each of these representations?

- Truth table (TT)

- Sum-of-products (SOP)

- Product-of-sums (POS)

- Binary decision diagram (BDD)

F = ab+cd

F = (a+c)(a+d)(b+c)(b+d)

- And-inverter graph (AIG)

- Logic network (LN)

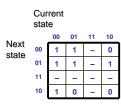

## **Representation Overview**

- TT are the natural representation of logic functions

- Not practical for large functions

- Still good for functions up to 16 variables

- SOP is widely used in synthesis tools since 1980's

- More compact than TT, but not canonical

- Can be efficiently minimized (SOP minimization by Espresso, ISOP computation) and translated into multi-level forms (algebraic factoring)

- BDD is a useful representation discovered around 1986

- Canonical (for a given function, there is only one BDD)

- Very good, but only if (a) it can be constructed, (b) it is not too large

- Unreliable (non-robust) for many industrial circuits

- AIG is an up-and-coming representation!

- Compact, easy to construct, can be made "canonical" using a SAT solver

- Unifies the synthesis/mapping/verification flow

- The main reason to give this talk ©

### **Historical Perspective**

#### What are Typical Transformations?

- Typical transformations of representations

- For SOP, minimize cubes/literals

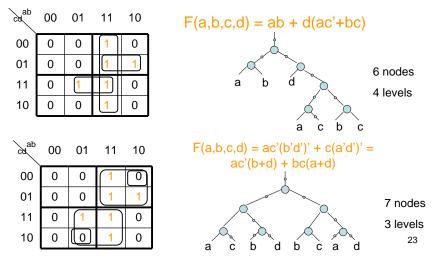

- For BDD, minimize nodes/width

- For AIG, restructure, minimize nodes/levels

- For LN, restructure, minimize area/delay

#### What Representation to Use?

- For small functions (up to 16 inputs)

TT works the best (local transforms, decomposition, factoring, etc.)

For medium-sized functions (16-100 inputs)

In some cases, BDDs are still used (reachability analysis)

Typically, it is better to represent as AIGs

Translate AIG into CNF and use SAT solver for logic manipulation

Sometimes need interpolation or SAT assignment enumeration

For large industrial circuits (>100 inputs, >10,000 gates)

Traditional LN representation is not efficient

AIGs work remarkably well

Lead to efficient synthesis

Are a natural representation for technology mapping

- Easy to translate into CNF for SAT solving

- Etc.

**Algorithmic Paradigms**

- Divide-and-conquer

- Traversal, windowing, cut computation

- Guess-and-check

- Bit-wise simulation

- Reason-and-prove

- Boolean satisfiability

#### Traversal

- Traversal is visiting nodes in the network in some order

- Topological order visits nodes from PIs to POs

- Each node is visited after its fanins are visited

- Reverse topological order visits nodes from POs to PIs

- Each node is visited after its fanouts are visited

Traversal in a topological order

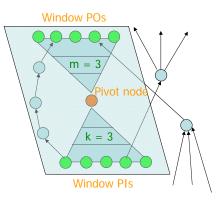

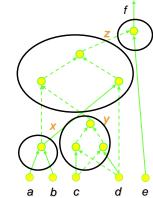

# Windowing

- Definition

- A window for a node is the node's context, in which an operation is performed

- A window includes

- k levels of the TFI

- m levels of the TFO

- all re-convergent paths between window PIs and window POs

14

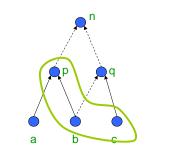

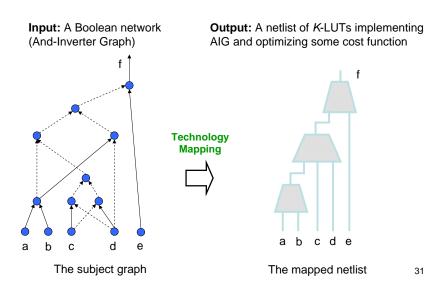

#### Structural Cuts in AIG

A cut of a node *n* is a set of nodes in transitive fan-in such that every path from the node to PIs is blocked by nodes in the cut.

A k-feasible cut means the size of the cut must be *k* or less.

The set  $\{p, b, c\}$  is a 3-feasible cut of node n. (It is also a 4-feasible cut.)

*k*-feasible cuts are important in FPGA mapping because the logic between root n and the cut nodes  $\{p, b, c\}$  can be replaced by a *k*-LUT

15

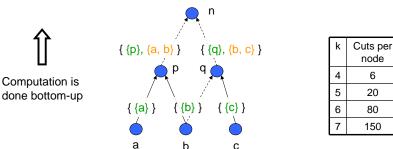

#### **Cut Computation**

#### { {n}, {p, q}, {p, b, c}, {a, b, q}, {a, b, c} }

The set of cuts of a node is a 'cross product' of the sets of cuts of its children. Any cut that is of size greater than k is discarded.

#### **Bitwise Simulation**

- Assign particular (or random) values at the primary inputs

- Multiple simulation patterns are packed into 32- or 64-bit strings

- Perform bitwise simulation at each node

- Nodes are ordered in a topological order

- Works well for AIG due to

- The uniformity of AND-nodes

- Speed of bitwise simulation

- Topological ordering of memory used for simulation information

17

## **Boolean Satisfiability**

- Given a CNF formula φ(x), satisfiability problem is to prove that φ(x) ≡ 0, or to find a counter-example x' such that φ(x') ≡ 1

- Why this problem arises?

- If CNF were a canonical representation (like BDD), it would be trivial to answer this question.

- But CNF is not canonical. Moreover, CNF can be very redundant, so that a large formula is, in fact, equivalent to 0.

- Looking for a satisfying assignment can be similar to searching for a needle in the hay-stack.

- The problem may be even harder, if there is no needle there!

18

20

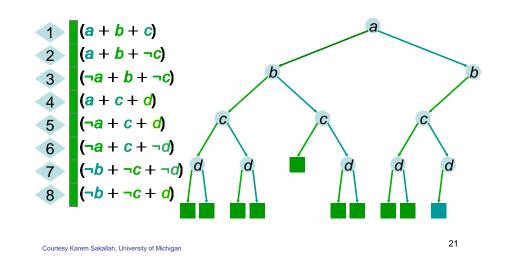

# Example (Deriving CNF)

CNF

ab (a+b+c)cd 00 01 11 10 (a + b + c')00 (a' + b + c')01 (a + c + d)11 10 (a' + c + d)(a' + c + d')Cube: bcd' (b' + c' + d')Clause: b' + c' + d(b' + c' + d)

## SAT Solver

#### • SAT solver types

- CNF-based, circuit-based

- Complete, incomplete

- DPLL, saturation, etc.

#### • Applications in EDA

- Verification

- Equivalence checking

- Model checking

- Synthesis

- Circuit restructuring

- Decomposition

- False path analysis

- Routing

- A lot of magic is used to build an efficient SAT solver

- Two literal clause watching

- Conflict analysis with clause recording

- Non-chronological backtracking

- Variable ordering heuristics

- Random restarts, etc

- The best SAT solver is MiniSAT (http://minisat.se/)

- Efficient (won many competitions)

- Simple (600 lines of code)

- Easy to modify and extend

- Integrated into ABC

## Example (SAT Solving)

# (2) And-Inverter Graphs (AIG)

- Definition and examples

- Several simple tricks that make AIGs work

- Sequential AIGs

- Unifying representation

- A typical synthesis application: AIG rewriting

AIG Definition and Examples

AIG is a Boolean network composed of two-input ANDs and inverters.

## Three Simple Tricks

- Structural hashing

- Makes sure AIG is stored in a compact form

- Is applied during AIG construction

- Propagates constants

- Makes each node structurally unique

- Complemented edges

- Represents inverters as attributes on the edges

- Leads to fast, uniform manipulation

- Does not use memory for inverters

- Increases logic sharing using DeMorgan's rule

- Memory allocation

- Uses fixed amount of memory for each node

- Can be done by a simple custom memory manager

- Even dynamic fanout manipulation is supported!

- Allocates memory for nodes in a topological order

- Optimized for traversal in the same topological order

Small static memory footprint for many applications

- Small static memory loophil for many ap

Computes fanout information on demand

Without hashing

22

With hashing<sup>24</sup>

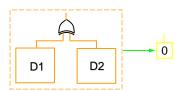

## Sequential AIGs

- Sequential networks have memory elements in addition to logic nodes

- Memory elements are modeled as D-flip-flops

- Initial state  $\{0,1,x\}$  is assumed to be given

- Several ways of representing sequential AIGs

- Additional PIs and POs in the combinational AIG

- Additional register nodes with sequential structural hashing

- Sequential synthesis (in particular, retiming) annotates registers with additional information

- Takes into account register type and its clock domain

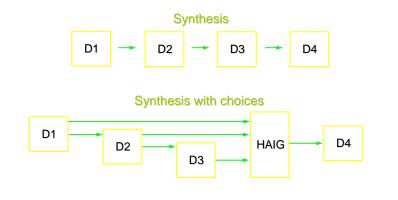

## AIG: A Unifying Representation

- An underlying data structure for various computations

- Rewriting, resubstitution, simulation, SAT sweeping, induction, etc. are based on the same AIG manager

- A unifying representation for the whole flow

- Synthesis, mapping, verification use the same data structure

- Allows multiple structures to be stored and used for mapping

- The main functional representation in ABC

- A foundation of new logic synthesis

# (3) AIG-Based Solutions

- Synthesis

- Mapping

- Verification

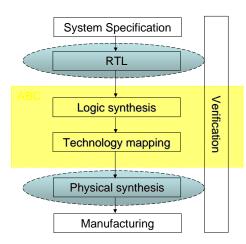

## **Design Flow**

25

# **Combinational Synthesis**

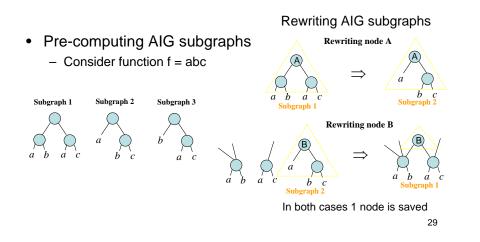

• AIG rewriting minimizes the number of AIG nodes without increasing the number of AIG levels

## **AIG-Based Solutions (Mapping)**

## AIG-Based Solutions (Synthesis)

- Restructures AIG or logic network by the following transforms

- Algebraic balancing

- Rewriting/refactoring/redecomposition

- Resubstitution

- Minimization with don't-cares, etc.

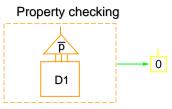

## **Formal Verification**

- Equivalence checking

Takes two designs and makes a miter (AIG)

- Model checking *safety* properties

- Takes design and property and makes a miter (AIG)

The goals are the same: to transform AIG until the output is proved constant 0

(ABC won model checking competitions in recent years)

#### Equivalence checking

## ABC vs. Other Tools

- Industrial

- + well documented, fewer bugs

- black-box, push-button, no source code, often expensive

- SIS

- + traditionally very popular

- data structures / algorithms outdated, weak sequential synthesis

- VIS

- + very good implementation of BDD-based verification algorithms

- not meant for logic synthesis, does not feature the latest SAT-based implementations

- MVSIS

- + allows for multi-valued and finite-automata manipulation

- not meant for binary synthesis, lacking recent implementations

37

# How Is ABC Different From SIS?

**Equivalent AIG in ABC**

AIG is a Boolean network of 2-input AND nodes and inverters (dotted lines) <sup>38</sup>

# One AIG Node – Many Cuts

- Combinational AIG .

- Manipulating AIGs in ABC

- Each node in an AIG has many cuts

- Each cut is a different SIS node

- No a priori fixed boundaries

- Implies that AIG manipulation with cuts is equivalent to working on many Boolean networks at the same time

#### Comparison of Two Syntheses

•

#### "Classical" synthesis

- Boolean network

- Network manipulation (algebraic)

- Elimination

- Factoring/Decomposition

- Speedup

- Node minimization

- Espresso

- Don't cares computed using BDDs

- Resubstitution

- Technology mapping

- Tree based

#### ABC "contemporary" synthesis

- AIG network

- DAG-aware AIG rewriting (Boolean) – Several related algorithms

- Rewriting

- Refactoring

- Balancing

- Speedup

- Node minimization

- Boolean decomposition

- Don't cares computed using simulation and SAT

- Resubstitution with don't cares

- Technology mapping

- Cut based with choice nodes 40

Different cuts for the same node

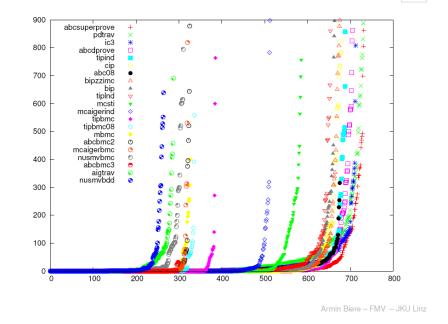

#### **Model Checking Competition**

| 🗄 Hardware Model Checking Competiti 🔅 |                                                                                                    |                |                                                            |  |

|---------------------------------------|----------------------------------------------------------------------------------------------------|----------------|------------------------------------------------------------|--|

| 44/2/                                 | Result                                                                                             | s              |                                                            |  |

| Mcc                                   | The results                                                                                        | have been pres | ented at <u>HWVW'10</u> with the following <u>slides</u> . |  |

| 1700                                  | The winner                                                                                         | is are:        |                                                            |  |

| HWMCC'10                              | ALL                                                                                                | abcsuperprove  | University of California, Berkeley                         |  |

| Benchmarks                            | SAT                                                                                                | abcbmc2        | University of California, Berkeley                         |  |

| Organizers<br>Results                 | UNSAT                                                                                              | pdtrav         | Politecnico di Torino                                      |  |

| Rules                                 | For more information on the set-up please consult the <u>slides</u> of the <u>HWVW/10</u> .        |                |                                                            |  |

|                                       | More details can be found in the following files: table.ds, table.csv, details.bt, and checked.bt. |                |                                                            |  |

|                                       |                                                                                                    |                |                                                            |  |

Cactus all Instances

# Further Reading: ABC Tutorial

- For more information, please refer to

- R. Brayton and A. Mishchenko, "ABC: An academic industrial-strength verification tool", Proc. CAV'10, Springer, LNCS 6174, pp. 24-40.

- http://www.eecs.berkeley.edu/~alanmi/publications/20 10/cav10\_abc.pdf

## Summary

- Introduced problems in logic synthesis

Representations and computations

- Described And-Inverter Graphs (AIGs)

- The foundation of innovative synthesis

- Overviewed AIG-based solutions

- Synthesis, mapping, verification

- Introduced ABC

- Differences, fundamentals, programming

22/26

# Assignment: Using ABC

- Using BLIF manual http://www.eecs.berkeley.edu/~alanmi/publicatio ns/other/blif.pdf

create a BLIF file representing a 2-bit multiplier

- Perform the following sequence:

- read the file into ABC (command "read")

- check statistics (command "print\_stats")

- visualize the network structure (command "show")

- convert to AIG (command "strash")

- visualize the AIG (command "show")

- convert to BDD (command "collapse")

- visualize the BDD (command "show\_bdd")

45

## Assignment: Programming ABC

- Write a procedure in ABC environment to iterate over the objects of the network and list the ID number, type, and fanin object IDs for each object on a separate line. Integrate this procedure into ABC, so that running command "test" would invoke your code, and print the result. Compare the print-out of the new command "test" with the result of command "show" for the multiplier example above

- Comment 1: For commands "show" and "show\_bdd" to work, please download the binary of software "dot" from GraphViz webpage and put it in the same directory as the ABC binary or anywhere else in the path: <u>http://www.graphviz.org</u>

- Comment 2: Make sure GSview and Ghostscript are installed on your computer. <u>http://pages.cs.wisc.edu/~ghost/gsview/</u>

46

# Programming Help

Example of code to iterate over the objects void Abc\_NtkCleanCopy( Abc\_Ntk\_t \* pNtk )

{

Abc\_Obj\_t \* pObj;

int i;

```

Abc_NtkForEachObj( pNtk, pObj, i )

pObj->pCopy = NULL;

```

Example of code to create new command "test" Call the new procedure (say, Abc\_NtkPrintObjs) from Abc\_CommandTest() in file "abc\src\base\abci\abc.c" Abc\_NtkPrintObjs( pNtk );