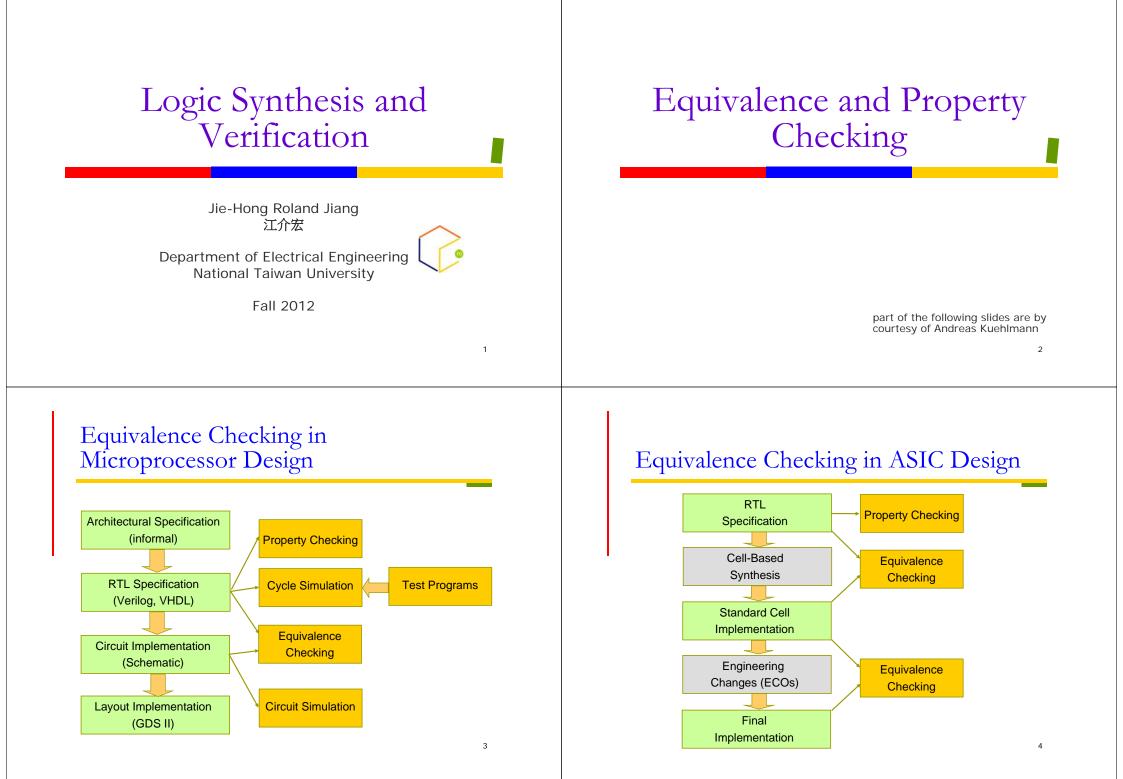

## Finite State Machine Model

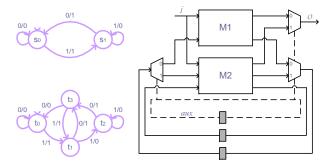

# Sequential Equivalence Checking

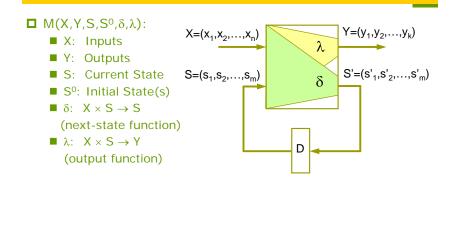

Definition: Two FSMs  $M_1$  and  $M_2$  are functionally equivalent iff the product machine  $M_1 \times M_2$  produces a constant 0 sequence for all valid input sequences { $X^{(1)}, ..., X^{(t)}$ }

# General Approach to SEC

## Sequential Equivalence Checking

7

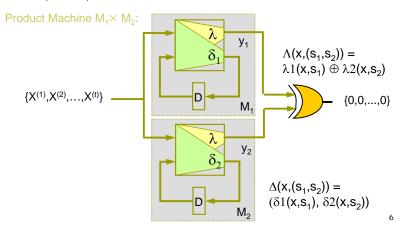

## Soundness and Completeness

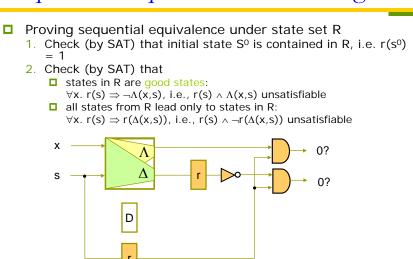

## With a candidate state set R we can

- prove equivalence that means the method is "sound"

- we will not produce "false positives"

- but not disprove equivalence

that means the method is "incomplete"

we may produce "false negatives"

## Inductive State Set Derivation

#### **Reachability analysis:**

state traversal until no more states can be explored

forward vs. backward

explicit vs. implicit (symbolic)

#### **Relying on the design methodology to provide R**:

- equivalent state encoding in both machines

- synthesis tool provides hint for R from sequential optimization

- manual register correspondence

automatic register correspondence

#### Combination of them

10

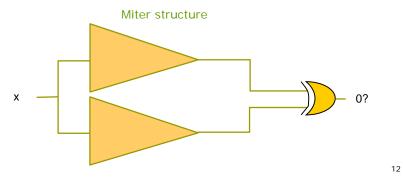

## Combinational EC

- Industrial equivalence checkers almost exclusively use a combinational EC paradigm

- sequential EC is too complex, can only be applied to design with a few hundred state bits

- combinational methods scale linearly with the design size for a given fixed size and "functional complexity" of the individual cones

- **I** Still, pure BDDs and plain SAT solver cannot handle all cones

- BDDs can be built for about 80% of the cones of high-speed designs

- less for complex ASICs

- plain SAT blows up on a "miter" structure

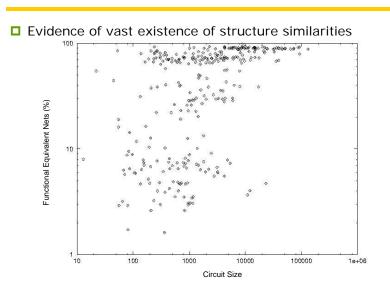

- Contemporary method highly exploit structural similarity of designs to be compared

## Combinational EC

## Basic methods:

- random simulation, good for finding mis-compares

- BDD-based with modifications

- structural SAT-based with modifications

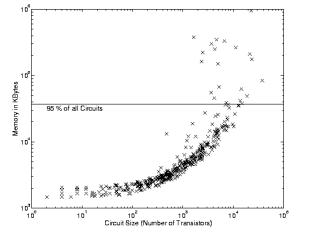

## Combinational EC

Memory statistics of BDD-based EC on a PowerPC processor design

13

15

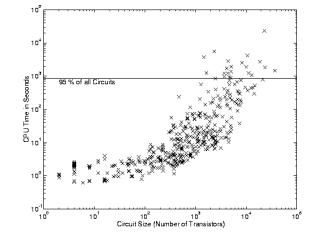

## Combinational EC

Runtime statistics of BDD-based EC on a PowerPC processor design

14

## Combinational EC

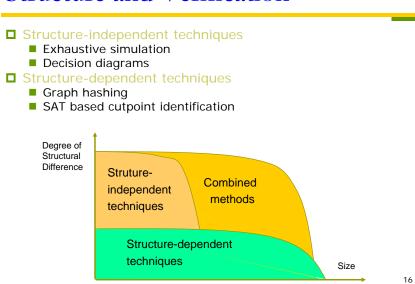

# Structure and Verification

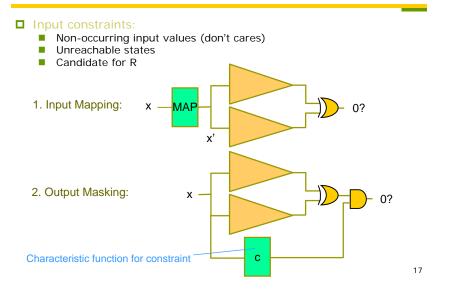

# Constrained EC

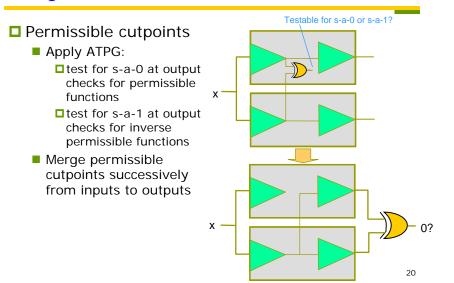

# Cutpoint-Based EC

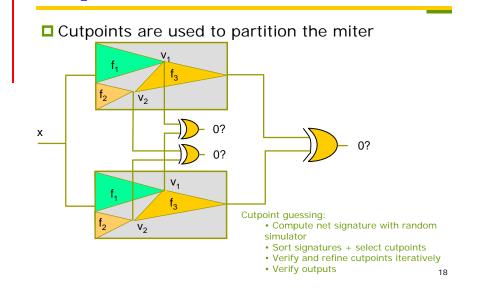

# Cutpoint-Based EC

## □ False negatives

Outputs may miscompare for invalid cutpoint values <sup>xy</sup> 00 10 11 01 vz Constraint: 00  $c = (v \equiv y + z)$ 01 1 <sup>xy</sup> 00 10 11 01 11 1 1 1 vz 10 1 1 1 out 00 1 1 01 <sup>xy</sup> 00 10 11 01 11 1 1 1 1 vz 00 10 1 1 01 11 1 1 1 10 1 1 1

19

What can we do about false negatives:

• constrain input space to  $c = (v \equiv y+z)$

• if v in SUPPORT(out), then out = compose(out, v,  $f_v$ )

## Cutpoint-Based EC

- If combinational verification paradigm fails (e.g. we have no name matching)

- Two options:

- Run general sequential verification based on state traversal

- Very expensive but most general

- Try to match registers automatically

Structural register correspondence

Functional register correspondence

## Register Correspondence

- Find registers in product machine that implement identical or complemented function

- These are matching registers in the two FSMs under comparison

- BUT: might be more, we may have redundant registers

- □ Definition: A register correspondence  $RC \subseteq \underline{s} \times \underline{s}$  is an equivalence relation in the set of registers  $\underline{s}$

- Can be extended to also include complemented functions

- A register correspondence can be used as a candidate for R:

$$r(s) = \prod_{\forall (s^i, s^j) \in RC} (s^i \equiv s^j) \qquad RC \subseteq \underline{s} \times \underline{s}$$

22

## Register Correspondence

```

■ Algorithm REGISTER_CORRESPONDENCE {

RC' = \{(s^i, s^j) | s^i_0 = s^j_0\}

//start with registers with identical initial values

do {

RC = RC'

r(s) = \Pi_{\forall(s^i,s^j) \in RC} (s^i = s^j)

RC' = \{(s^i, s^j) | (s^i, s^j) \in RC \land \delta^i(x, s) = \delta^j(x, s) \land r(s)\}

//\delta^i is the transition function of s^i

} while (RC' != RC)

return RC

}

```

#### In essence

- The algorithm starts with an initial partitioning with two equivalence classes, one for each initial value

- The algorithm computes iteratively the next-state function, assuming that the RC is correct

- if yes, fixed point is reached and RC returned

- □ if no, split equivalence classes along the mis-compares

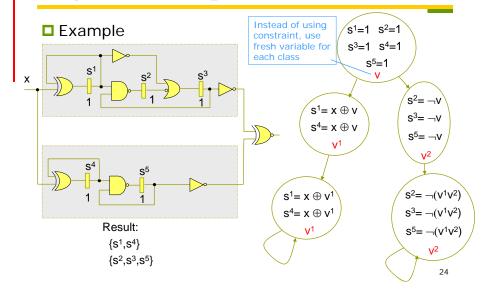

## Register Correspondence

# Register Correspondence

## □ Potential problems:

- In case of mis-comparing designs

- Effect of mis-compared cone may ripple through entire algorithm and split all equivalence classes until they contain only single registers

Difficult to debug since no hint of error location

## Solution:

- Relax equivalence criteria

- E.g. structural register correspondence algorithm based on support set of registers

- Combine with name mapping, functional/structural criteria

#### 25

# Sequential EC

- □ In case that combinational EC model fails:

- Use generalized register correspondence to also consider retiming

In essence, use all internal nets as candidates for possible matches

## □ Worst case: general sequential verification

- Prove that the output of the product machine is not satisfiable (sequentially)

- Special case of general property checking

# Sequential EC

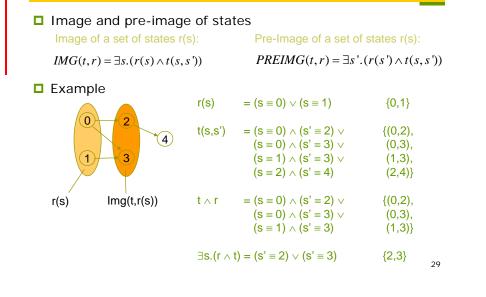

## State traversal

- Forward

- Start from initial state(s)

Traverse forward to check whether "bad" state(s) is reachable

- Backward

- □ Start from bad state(s)

- Traverse backward to check whether initial state(s) can reach them

- Hybrid

- Compute over-approximation of reachable states by forward traversal

- □ For all bad states in overapproximation, start backward traversal to see whether initial state can reach them

# Sequential EC

## Sequential EC

| gorithm TRAVERSE_FORWARD(t, $\lambda$ ,S0) { reached = $\emptyset$ |                        |

|--------------------------------------------------------------------|------------------------|

| current = S0                                                       | // start from init     |

| <pre>while (reached ≠ (reached ∨ current)) {</pre>                 | // fixed point         |

| reached = reached v current                                        | // add new states      |

| <pre>next = IMG(t,current)</pre>                                   | // one step transition |

| current = next                                                     | // rename variable     |

| }                                                                  |                        |

| <b>return</b> $\exists x.(\lambda(x,s) \land reached)$             |                        |

|                                                                    |                        |

| Iteration: | 1     | 2       | 3         |

|------------|-------|---------|-----------|

| Reached:   | {0}   | {0,1,2} | {0,1,2,3} |

| Current:   | {0}   | {1,2}   | {1,2,3}   |

| Next:      | {1,2} | {1,2,3} | {0,1,2,3} |

30

## Sequential EC

| current = $\exists x. (\lambda(x,s)=1)$ // start from bad                                                           |

|---------------------------------------------------------------------------------------------------------------------|

|                                                                                                                     |

| <pre>while (reached ≠ (reached ∨ current)) { // fixed point<br/>reached = reached ∨ current // add new states</pre> |

| <pre>previous = PRE_IMG(t,current) // one step transition<br/>current = previous // rename variable</pre>           |

| return (S0 ^ reached) }                                                                                             |

#### Example

|     |     | Iteration: | 1   | 2     | 3       |

|-----|-----|------------|-----|-------|---------|

|     | 4   | Reached:   | {6} | {4,6} | {4,5,6} |

|     |     | Current:   | {6} | {4}   | {4,5}   |

| 3-2 | 5-6 | Previous:  | {4} | {4,5} | {4,5,6} |

## Sequential EC

## Explicit reachability analysis

- Represent states explicitly (e.g. as bit string) => limited capacity

- Use hashtable to find quickly whether state was reached before

- Image operation: simple simulation

- Preimage operation: SAT run

## Symbolic reachability analysis

- Represent states and transition relation symbolically

E.g. BDDs, circuits, DNF, etc.

- Use BDD operations to perform image and preimage operation (simple AND or AND\_EXIST)

- Lots of heuristic improvements to keep BDD size under control

Let R(s) be the characteristic function of the set of reachable states of the product FSM  $M_{1\times 2}$ obtained from forward reachability analysis. Then FSMs  $M_1$  and  $M_2$  are equivalent if and only if

$\lambda_{1\times 2}(x,s)\,\wedge\,R(s)$

is constant 0 for all valuations on input variables  $\boldsymbol{x}$  and state variables  $\boldsymbol{s}$

This can be checked in constant time for BDD

# Sequential EC

## Example

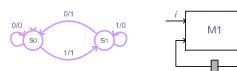

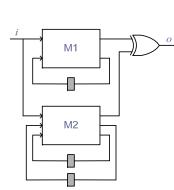

**To check:** The equivalence of  $M_1$  and  $M_2$

M2

# Sequential EC

## Example (cont'd)

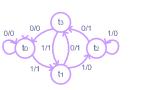

Construct product FSM of M<sub>1</sub> and M<sub>2</sub>

# Sequential EC

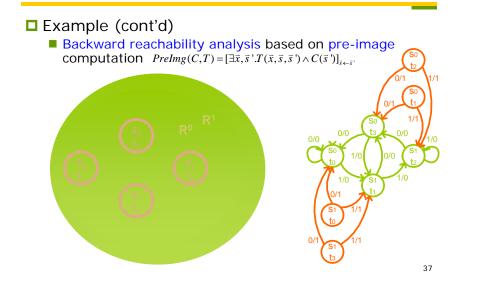

## Example (cont'd)

■ Forward reachability analysis based on image computation  $Img(C,T) = [\exists \bar{x}, \bar{s}T(\bar{x}, \bar{s}, \bar{s}') \land C(\bar{s})]_{s' \leftarrow \bar{s}}$

35

# Sequential EC

## Alternative approach beyond reachability analysis

- Based on state equivalence

- Two FSMs are equivalent if and only if their initial states are equivalent

- Two states of an FSM are equivalent if starting these two states the FSM behaves indistinguishably

- Explicit algorithm (based on state transition graph enumeration) is known

Used in state minimization where equivalent states must be identified

How about implicit algorithm (based on Boolean manipulation) ?

Sequential EC

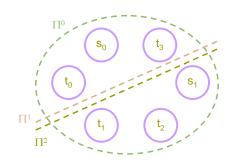

State partitioning based sequential EC

Construct and multiplexed FSM (disjoint union of the state graphs)

## Example

# Sequential EC

- State partitioning over multiplexed FSM

- Using BDD-based functional decomposition

110 0

111

$v_1 v_2$

# State partitioning based sequential EC BDD-based functional decomposition Bound set variables (top): state variables Free set variables (bottom): others Cutset: free-set nodes with incoming edges from bound-set nodes Paths leading to a node in the cutset form an equivalence class of states (for an iteration) Iterate functional decomposition over composed functions

## Sequential EC

# Example (cont'd)State partitioning

#### 42

## Sequential EC

Connection between reachability based SEC and state partitioning based SEC

Backward reachability analysis can be considered as state partitioning in the product state space

## Sequential EC

sequential circuits

## Summary

- Industrial EC checkers almost exclusively use an combinational EC paradigm even for sequential EC

Sequential EC is too complex and can only be applied to design with a few hundred state bits

- Structure similarity should be identified to simplify sequential EC

- Besides sequential equivalence checking, reachability analysis is useful in sequential circuit optimization

Recall in sequential optimization that unreachable states can be used as sequential don't cares to optimize a

43

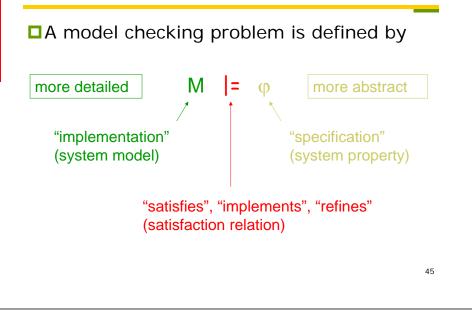

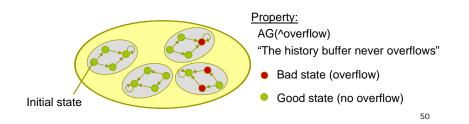

# Model Checking

## Model Checking

## $\square$ M |= $\phi$

- Check if system model M satisfies a system property  $\phi$

- System model M is described with a state transition system

finite state or infinite state

- Temporal property φ can be described with three orthogonal choices:

- 1.operational vs. declarative: automata vs. logic

- 2.may vs. must: branching vs. linear time

- 3.prohibiting bad vs. desiring good behavior: safety vs. liveness

Different choices lead to different model checking problems.

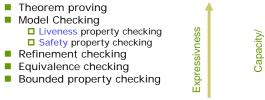

# Property Checking

- Assertion-based verification

- Properties are expressed as RTL annotations in terms or assertions ("This statement must hold true")

- E.g. AG(x=y) "For all paths from the initial state and all successor states x=y"

Degree of Automation

- Formal verification methods:

- Exhaustive, do not require simulation vectors

- □ Main methods:

- Safety property: Something "bad" will never happen

- Safety property violation always has a finite witness

if something bad happens on an infinite run, then it happens already on some finite prefix

- Example

- Two processes cannot be in their critical sections simultaneously

- Liveness property: Something "good" will eventually happen

- Liveness property violation never has a finite witness

- no matter what happens along a finite run, something good could still happen later

- Example

- Whenever process P1 wants to enter the critical section, provided process P2 never stays in the critical section forever, P1 gets to enter eventually

For finite state systems, liveness can be converted to safety!

# Safety Property Checking

- Safety property checking can be formulated as a reachability problem

Are bad states reachable from good states?

- Sequential equivalence checking can be considered as one kind of safety property checking

- M : product machine

- φ : all states reachable from initial states has output 0

# Safety Property Checking

#### Concept:

- Counter example has finite length

- Specification in terms of "bad behavior" that should not happen

- E.g. specify a state with a bad property or a bad output condition

- Handles 95% of practical properties

## Basic approach:

- Express property as formula on state and inputs

- Single reachability analysis sufficient to decide about correctness

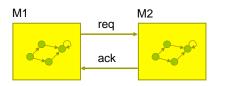

# Liveness Property Checking

#### Concept:

- Counter example has infinite length

- Specification in terms of "good behavior" that should always happen

- E.g. AG(req=>AF ack)

### Basic approach:

Nested reachability analysis according to formula

<u>Property:</u> AG(req=> AF ack) "A request from M1 will always be acknowledged by M2"

# Model Checking

- Data structure evolution in model checking

- State graph (late 70s-80s)

Problem size ~10<sup>4</sup> states

- BDD (late 80s-90s) symbolic model checking

Problem size ~10<sup>20</sup> states

Critical resource: memory

- SAT (late 90s-) bounded/unbounded model checking

GRASP, SATO, chaff, berkmin

- ■Problem size ~10<sup>100</sup> (?) states ■Critical resource: CPU time

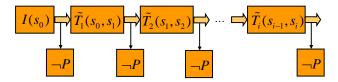

## Bounded Model Checking

- Bounded Model Checking (Biere, et al., TACAS 1999):

- Property checking method based on finite unfolding of transition relation interleaved with checks of the property

■ Sound: in its pure form no false positives are possible ■ Incomplete: cannot guarantee correctness of property

#### Basic method:

- CNF-based:

- Use CNF-based SAT solver to represent unfolding and proof UNSAT for correctness of property

- Circuit-based:

- Use ATPG-like reasoning to show untestability

#### Hybrid:

- Use circuit rewriting and SAT checking interleaved

- e.g. based on AND/INV graphs

53

## Bounded Model Checking

BMC for length kBMC<sub>k</sub> =  $i(s_0) \wedge t^k(s_0, s_k) \wedge \neg p(s_k)$

## BMC loop

```

Algorithm BMC(max_length){

forall 0 ≤ k < max_length do {

if(SAT(BMC<sub>k</sub>)) return FAIL

}

return SUCCESS;

}

```

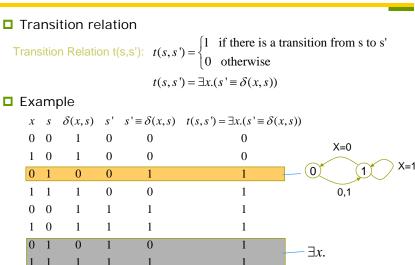

## Bounded Model Checking

## Notation

- Variables for current and next state: *s*, *s*'

- Predicate for transition relation: t(s,s')t(s,s')=1 iff there is a transition from s to s'

- Predicate for initial states: i(s)

I iff s is an initial state

- Predicate for property: p(s)

\$\Box\$p(s)=1 iff s satisfies property p

- Predicate for all paths of length k:

## $t^{k}(s_{0'}s_{k}) = \prod_{0 \le i < k} t(s_{i'}s_{i+1})$

□  $t^k(s_0, s_k) = 1$  iff there is a transition path of length k from  $s_0$  to  $s_k$

## Bounded Model Checking

## □ BMC unfolding

Time-frame expansion

#### Comments:

- Any SAT technique can be used for checking frames

- Combination with random simulation, parallel runs etc.

## Unbounded Model Checking

K-step induction [Sheeran, FMCAD 2000]

Assert correctness of properties proven for previous frames

$tp^{k}(s_{0},s_{k}) = \bigwedge_{0 \le i \le k} p(s_{i}) \wedge t(s_{i},s_{i+1})$

Simple path constraint

No state visited twice

$tp_{simple}^{k}(s_{0}, s_{k}) = \bigwedge_{0 \le i < k} p(s_{i}) \land t(s_{i}, s_{i+1}) \land \bigwedge_{0 \le i < j \le k} s_{i} \ne s_{j}$

K-step inductiveness

In addition to BMC<sub>k</sub> check also

$inv^k = tp^k(s_0, s_k) \wedge \neg p(s_k)$

- □ Interpolation [McMillan, CAV 2003]

- SAT-based model checking without unrolling [Bradley, VMCAI 2011]

57

# Model Checking

## Summary

- Temporal logic is a variation of mathematical logic and is concerned with temporal reasoning

Developed since 1970's

- Model checking is concerned with algorithmic verification of temporal properties

Developed since 1980's

Hardware model checking techniques are being applied in the software domain

### Reference

- K. McMillan. Symbolic Model Checking. Kluwer Academic Publishers, 1993

- M. Clarke, O. Grumberg, and D. Peled. *Model Checking*. MIT Press, 1999