# Switching Circuits & Logic Design

Jie-Hong Roland Jiang 江介宏

Department of Electrical Engineering National Taiwan University

Fall 2013

# §14 Derivation of State Graphs and Tables

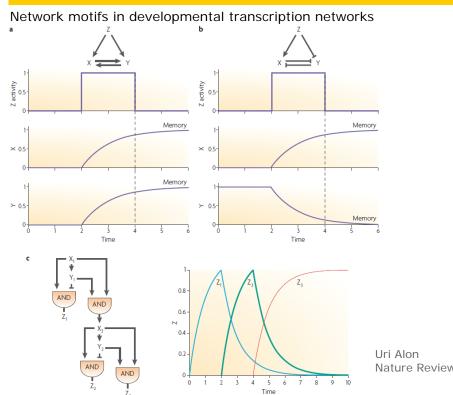

Nature Reviews Genetics, June 2007

# Outline

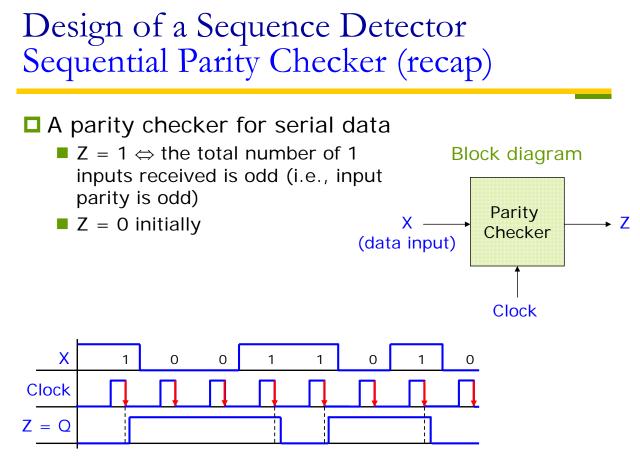

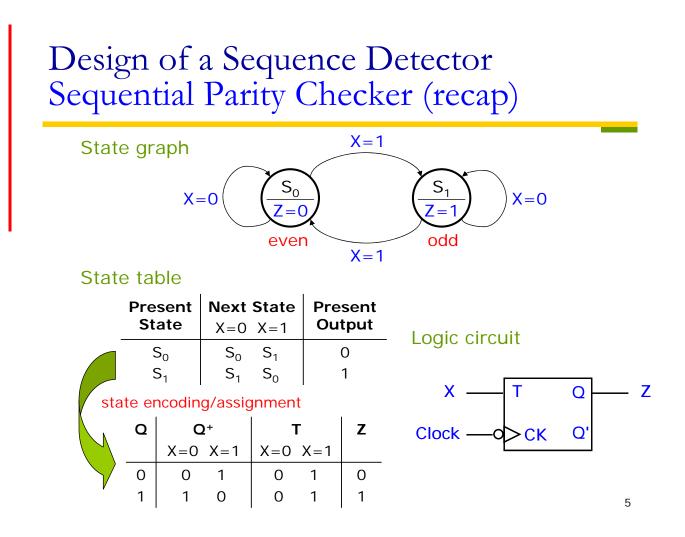

Design of a sequence detector

More complex design problems

Guidelines for construction of state graphs

Serial data code conversion

Alphanumeric state graph notation

Conversion between Mealy and Moore State Graphs

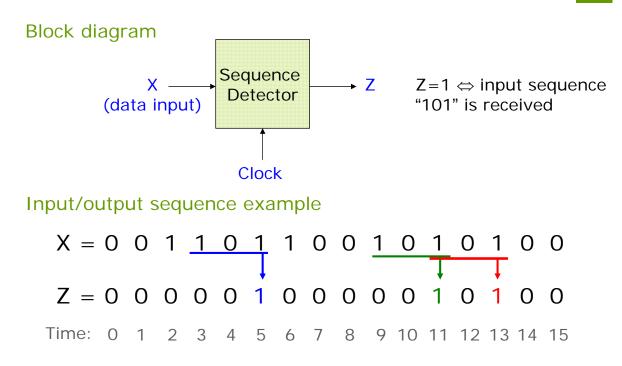

### Design of a Sequence Detector {101}-Sequence Detector

### Design of a Sequence Detector {101}-Sequence Detector

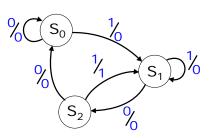

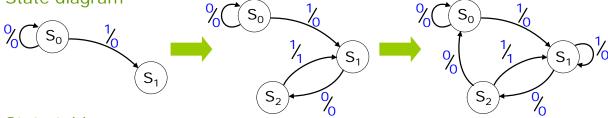

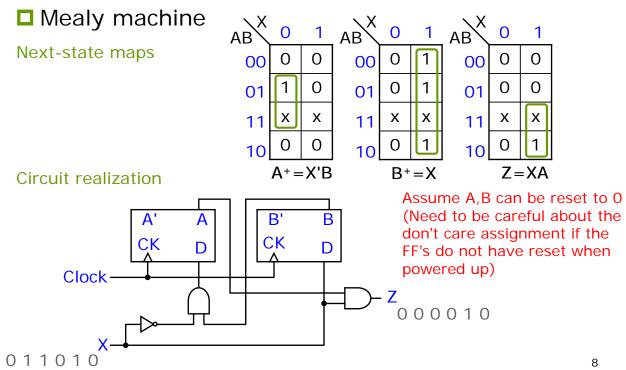

#### Mealy machine

State diagram

#### State table

|                      |                |                | Pres | sent |    | A+  | B+  |     | Z   |

|----------------------|----------------|----------------|------|------|----|-----|-----|-----|-----|

| Present              | Next           | State          | Out  | put  | AB | X=0 | X=1 | X=0 | X=1 |

| State                | X=0            | X=1            | X=0  | X=1  | 00 | 00  | 01  | 0   | 0   |

| S <sub>0</sub>       | S <sub>0</sub> | S₁             | 0    | 0    | 01 | 10  | 01  | 0   | 0   |

| $S_1^{\circ}$        | $S_2$          | S <sub>1</sub> | 0    | 0    | 10 | 00  | 01  | 0   | 1   |

| $S_2$                | S <sub>0</sub> | S <sub>1</sub> | 0    | 1    | 11 | -   | -   | -   | -   |

| S <sub>0</sub> : ini | tial stat      | te             |      |      |    |     |     |     |     |

$S_1$ : sequence ending with 1 received

S<sub>2</sub>: sequence ending with 10 received

## Design of a Sequence Detector {101}-Sequence Detector

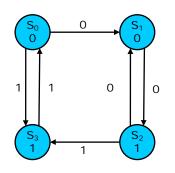

### Design of a Sequence Detector {101}-Sequence Detector

I

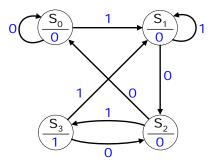

□ Moore machine

State table

| Present                                                   | Next                       | State                                                    | Present<br>Output |                      | A+                   | A <sup>+</sup> B <sup>+</sup> |             |  |

|-----------------------------------------------------------|----------------------------|----------------------------------------------------------|-------------------|----------------------|----------------------|-------------------------------|-------------|--|

| State                                                     | X=0                        | X=1                                                      | Z                 | AB                   | X=0                  | X=1                           | Z           |  |

| $ \begin{array}{c} S_0 \\ S_1 \\ S_2 \\ S_3 \end{array} $ | $S_0 \\ S_1 \\ S_2 \\ S_3$ | $egin{array}{c} S_1 \ S_2 \ S_0 \ S_1 \ S_1 \end{array}$ | 0<br>0<br>0<br>1  | 00<br>01<br>11<br>10 | 00<br>11<br>00<br>11 | 01<br>01<br>10<br>01          | 0<br>0<br>1 |  |

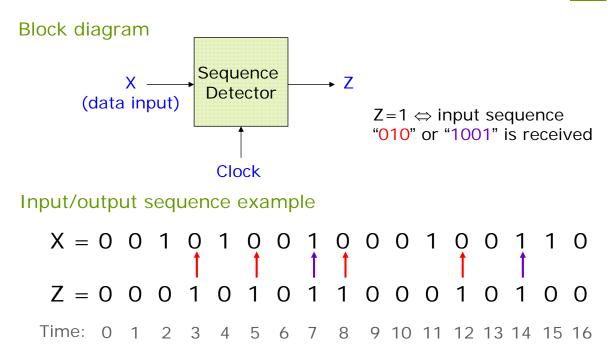

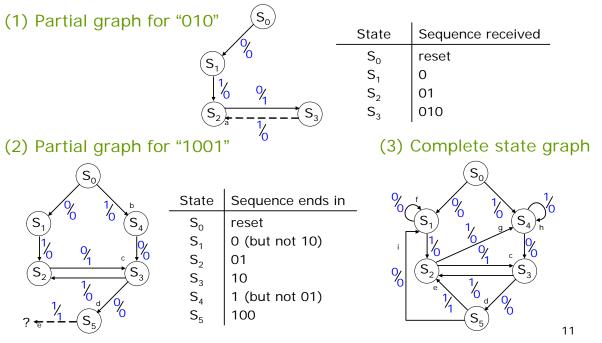

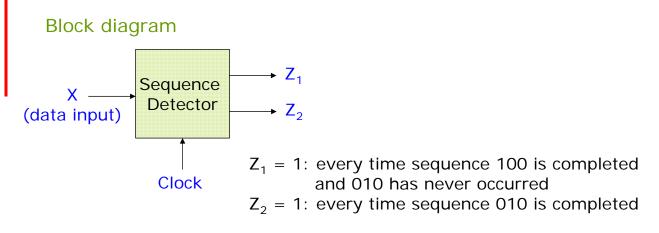

# More Complex Design Problems {010,1001}-Sequence Detector

# More Complex Design Problems {010,1001}-Sequence Detector

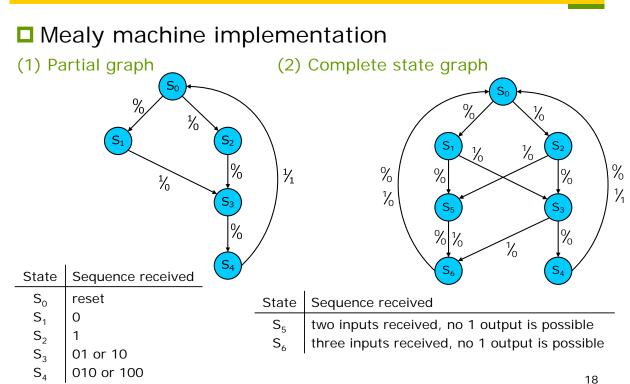

#### Mealy machine implementation

More Complex Design Problems {010,1001}-Sequence Detector

Exercise

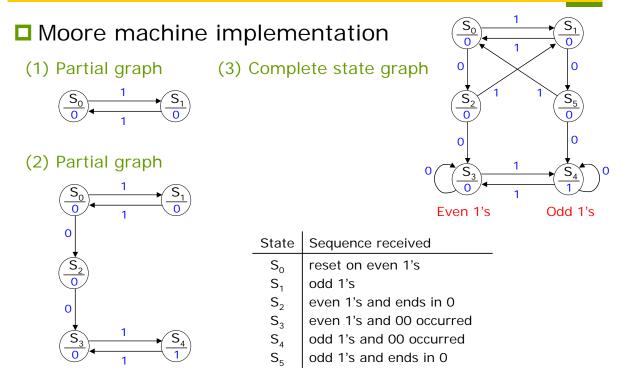

Moore machine implementation

#### More Complex Design Problems Modified Parity Sequence Detector

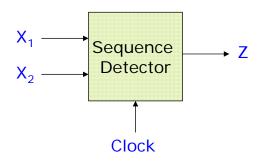

Block diagram

$Z=1 \Leftrightarrow$  the total number of 1's received is odd and at least two consecutive O's have been received

#### Input/output sequence example

| Χ = | 1 (   |     |   |   |     |     |     |   |     |  |

|-----|-------|-----|---|---|-----|-----|-----|---|-----|--|

|     | bbo   | ode | b |   | odd | odd | odd |   | odd |  |

| Ζ = | (0) 0 | 0   | ( | ) | 0   | 0   | 1   | 0 | 1   |  |

## More Complex Design Problems Modified Parity Sequence Detector

#### More Complex Design Problems Modified Parity Sequence Detector

Exercise

Mealy machine implementation

#### 15

## Construction of State Graphs

#### Guidelines

- 1. Construct sample input/output sequences

- 2. Determine under what conditions, if any, the circuit should reset to its initial state

- 3. If only one or two sequences lead to a nonzero output, construct a partial state graph for those sequences

- Alternatively, determine what sequences or groups of sequences must be remembered by the circuit and set up states accordingly

- 5. Each time an arrow is added, determine whether it can go to one of the previously defined states or whether a new state must be added

- 6. Check there is only one outgoing edge leaving each state for each input value

- 7. Test the completed graph and make sure correct

## Construction of State Graphs Example 1

#### **Block diagram**

$Z=1 \Leftrightarrow$  input sequence 0101 or 1001 occurs

The circuit examines groups of 4 consecutive inputs, and resets after every 4 inputs

#### Input/output sequence example

X = 0101 0010 1001 0100 Z = 0001 | 0000 | 0001 | 0000

## Construction of State Graphs Example 1

### Construction of State Graphs Example 2 (omitted)

19

#### Input/output sequence example

Construction of State Graphs Example 2 (omitted) Mealy machine implementation (1) Partial graph (2) Complete state graph ‰ ‰ ‰ 1/0 ‰ ‰ ‰ ‰ % 10 % %1 1/00 ‰ ‰ ‰ ‰ ‰ % ‰  $\%_1$ S, ‰ ‰ % ‰ ‰ ‰ State Description %1  $S_0 \\ S_1 \\ S_2 \\ S_3 \\ S_4$ No progress on 100 No progress on 010 Progress of 1 on 100 No progress on 010 %1 010 has never Progress of 0 on 010 Progress of 10 on 100 occurred Progress of 0 on 010 No progress on 100 Progress of 1 on 100 Progress of 01 on 010  $\frac{1}{100}$ S<sub>5</sub> S<sub>6</sub> S<sub>7</sub> Progress of 0 on 010 010 has Progress of 01 on 010 occurred partial graph for 010 20 No progress on 010

### Construction of State Graphs Example 2 (omitted)

#### State table

| Present        | Next           | state          | Output Z <sub>1</sub> Z <sub>2</sub> |     |  |

|----------------|----------------|----------------|--------------------------------------|-----|--|

| State          | X=0 X=1        |                | X=0                                  | X=1 |  |

| S <sub>0</sub> | S <sub>3</sub> | S <sub>1</sub> | 00                                   | 00  |  |

| $S_1$          | $S_2$          | $S_1$          | 00                                   | 00  |  |

| S <sub>2</sub> | $S_3$          | S <sub>4</sub> | 10                                   | 00  |  |

| $S_3$          | S <sub>3</sub> | S <sub>4</sub> | 00                                   | 00  |  |

| S <sub>4</sub> | S <sub>5</sub> | $S_1$          | 01                                   | 00  |  |

| S <sub>5</sub> | S <sub>5</sub> | S <sub>6</sub> | 00                                   | 00  |  |

| S <sub>6</sub> | S <sub>5</sub> | S <sub>7</sub> | 01                                   | 00  |  |

| S <sub>7</sub> | S <sub>5</sub> | S <sub>7</sub> | 00                                   | 00  |  |

Construction of State Graphs Example 3 (omitted)

Block diagram

- Z remains a constant value unless one of the following input sequences occurs

- (a) Input sequence  $X_1X_2 = 01$ , 11 causes Z=0

- (b) Input sequence  $X_1X_2 = 10$ , 11 causes Z=1 (c) Input sequence  $X_1X_2 = 10$ , 01 causes Z to change value

- $(X_1X_2 = 01, 11 \text{ means } X_1 = 0, X_2 = 1 \text{ followed by } X_1 = 1, X_2 = 1)$

22

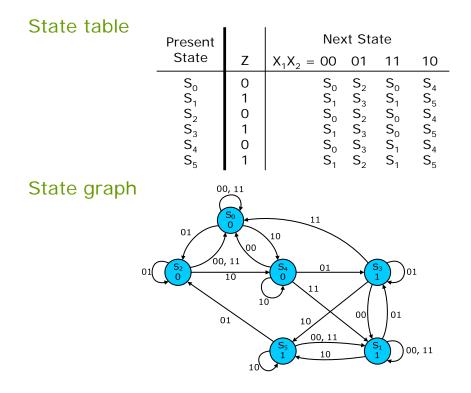

### Construction of State Graphs Example 3 (omitted)

#### Moore machine implementation

- Observation:

- Only the previous and present inputs (input sequence of length 2) will determine the output

- Unnecessary to use a separate state for 00 and 11 because neither input starts a sequence which leads to an output change

#### State designation

|   | Previous Input $(X_1X_2)$ | Output (Z) | State Designation |

|---|---------------------------|------------|-------------------|

| - | 00 or 11                  | 0          | S <sub>0</sub>    |

| _ | 00 or 11                  | 1          | S <sub>1</sub>    |

|   | 01                        | 0          | S <sub>2</sub>    |

| _ | 01                        | 1          | S <sub>3</sub>    |

|   | 10                        | 0          | S <sub>4</sub>    |

|   | 10                        | 1          | S <sub>5</sub>    |

|   |                           |            |                   |

#### Construction of State Graphs Example 3 (omitted)

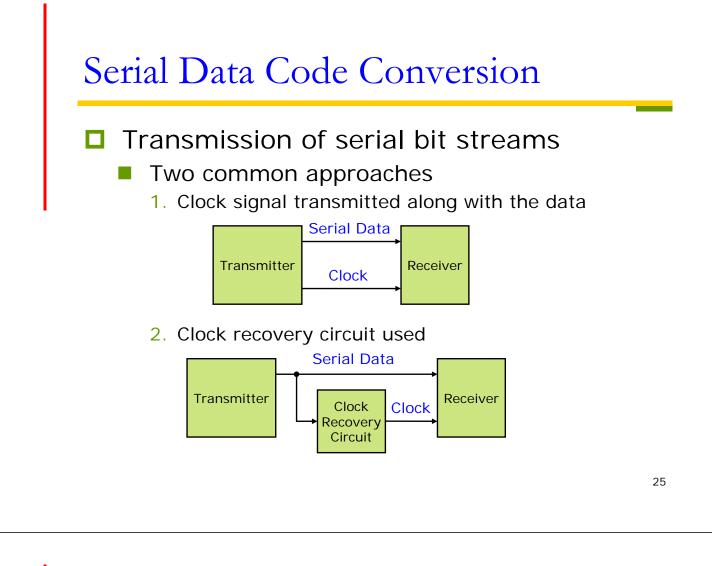

# Serial Data Code Conversion

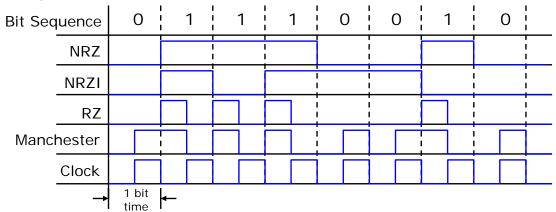

#### Four typical coding schemes

- NRZ (non-return-to-zero) code

- NRZI (non-return-to-zero-inverted) code

- RZ (return-to-zero) code

- Manchester code

Easy to recover the clock signal

#### Example

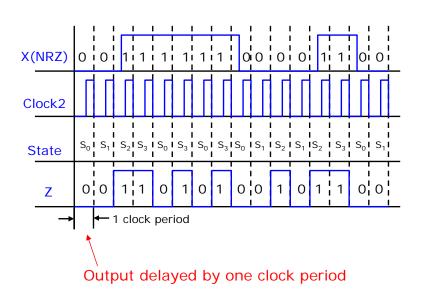

## Serial Data Code Conversion NRZ-Code to Manchester-Code

#### Mealy machine implementation Use Clock2, twice the frequency of the basic clock If the NRZ bit is 0 (1), it will be 0 (1) for two Clock2 periods NRZ data X Z Manchester Converte Clock2 data NRZ(X) 0 0 0 1 1 1 1 1 1 1 1 0 0 0 0 0 0 1 1 1 0 0 % Manchester 00 00 0 1 0 1 0 1 1 0 1¦1 1 1 (ideal) Clock2 % $\frac{1}{6}$ $S_0 | S_1 | S_0 | S_2 | S_0 | S_2 | S_0 | S_2 | S_0 | S_1 | S_0 | S_1 | S_0 | S_2 | S_0 | S_1$ State Z (actual) Next State Output Z Present 1 clock period glitch (false output) State X = 0X = 1X = 0X = 1 $S_1$ $S_0 \\ S_1 \\ S_2$ 1 0 $S_2$ $S_0$ 1 0 $S_0$ 27

### Serial Data Code Conversion NRZ-Code to Manchester-Code

#### Moore machine implementation

| Present                          | Next                    | State          | Present  |  |

|----------------------------------|-------------------------|----------------|----------|--|

| State                            | X = 0                   | X = 1          | Output Z |  |

| S <sub>0</sub><br>S <sub>1</sub> | $S_1$<br>$S_2$<br>$S_1$ | S <sub>3</sub> | 0        |  |

|                                  | S <sub>2</sub>          | -              | 0        |  |

| S <sub>2</sub><br>S <sub>3</sub> | $S_1$                   | $S_3$<br>$S_0$ | 1        |  |

| $S_3$                            | -                       | S <sub>0</sub> | 1        |  |

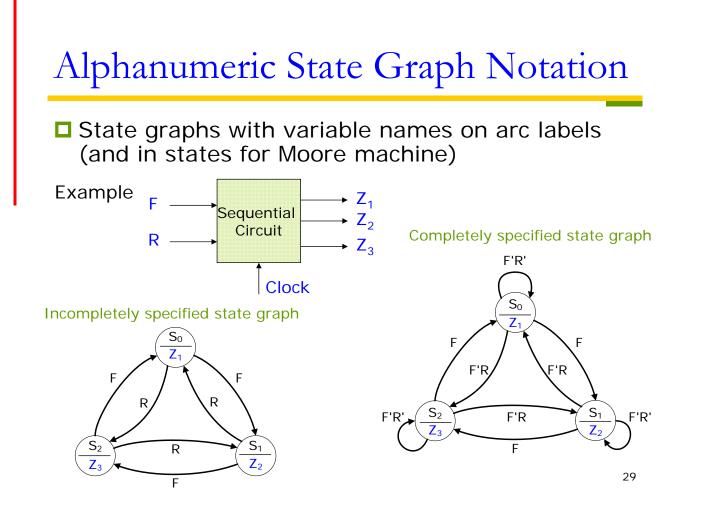

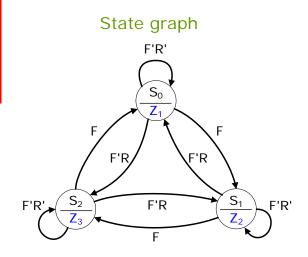

## Alphanumeric State Graph Notation

#### State table

| PS             |                | Output |       |       |             |

|----------------|----------------|--------|-------|-------|-------------|

|                | FR=00          | 01     | 10    | 11    | $Z_1Z_2Z_3$ |

| S <sub>0</sub> | S <sub>0</sub> | $S_2$  | $S_1$ | $S_1$ | 100         |

| $S_1$          | S <sub>1</sub> | $S_0$  | $S_2$ | $S_2$ | 010         |

| $S_2$          | S <sub>2</sub> | $S_1$  | $S_0$ | $S_0$ | 001         |

|                |                |        |       |       |             |

Check input signals (for every state): F + F'R + F'R' = F + F' = 1  $\Rightarrow$  Transition defined for every input combination  $F \cdot F'R = 0, F \cdot F'R' = 0, F'R \cdot F'R' = 0$  $\Rightarrow$  At most one next state for every input combination

# Alphanumeric State Graph Notation

- 1. ORing together all input labels on arcs outgoing from a state reduces to 1 (i.e., complete transition)

- For every input combination, at least one next state is defined

- ANDing together any pair of input labels on arcs outgoing from a state reduces to 0 (i.e., deterministic transition)

- For every input combination, no more than one next state is defined

- If both properties are true, then exactly one next state is defined

### Alphanumeric State Graph Notation

Convention for Mealy machine

- The label X<sub>i</sub>X<sub>j</sub>/Z<sub>p</sub>Z<sub>q</sub> on an arc means if X<sub>i</sub> and X<sub>j</sub> are 1 (we don't care what the other input values are), the outputs Z<sub>p</sub> and Z<sub>q</sub> are 1 (and the other outputs are 0)

- E.g., for a circuit with 4 inputs (X<sub>1</sub>, X<sub>2</sub>, X<sub>3</sub>, X<sub>4</sub>) and 4 outputs (Z<sub>1</sub>, Z<sub>2</sub>, Z<sub>3</sub>, Z<sub>4</sub>)

$X_1X_4'/Z_2Z_3$  is equivalent to 1--0/0110

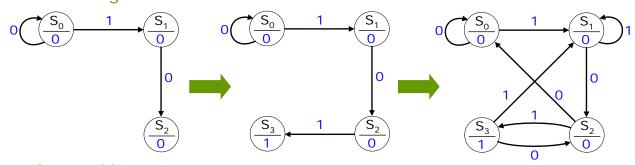

### Conversion between Mealy and Moore State Graphs

#### Convert Mealy to Moore

- 1. Push the output label on an edge to its next state (so delay introduced!)

- 2. If a state receives different output labels, duplicate the state such that every copy has exactly one output label

- Connect every edge properly to the state with correct output label

#### Convert Moore to Mealy

- 1. Distribute the output label of a state to its incoming edges

- 2. Simplify the state graph by merging equivalent states

Mealy-type implementation of a circuit can have fewer states than Moore-type implementation

### Conversion between Mealy and Moore State Graphs

Exercise