# Switching Circuits & Logic Design

Jie-Hong Roland Jiang 江介宏

Department of Electrical Engineering National Taiwan University

Fall 2013

## Outline

How to use a sequential circuit to control a sequence of operations in a digital system

Serial adder with accumulatorDesign of a parallel multiplier

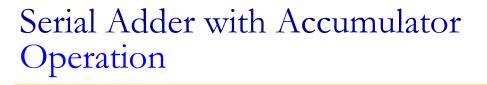

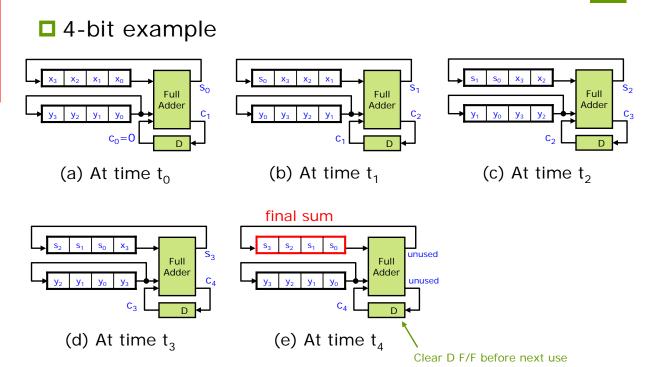

### Serial Adder with Accumulator Operation

#### 4-bit example

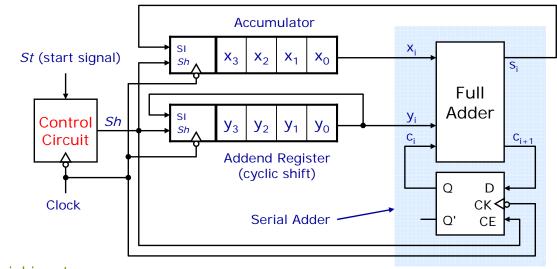

Serial Adder with Accumulator

#### Block diagram

SI: serial input St: start signal control signals Sh: shift signal

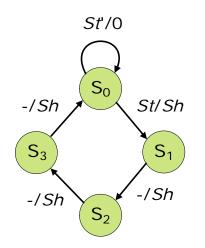

#### Serial Adder with Accumulator Control Circuit Design

#### State graph and state table

|                                  | Next S                                                               | tate           | Sh     |   |  |  |

|----------------------------------|----------------------------------------------------------------------|----------------|--------|---|--|--|

|                                  | St = 0                                                               | 1              | St = 0 | 1 |  |  |

| S <sub>0</sub>                   | S <sub>0</sub>                                                       | S <sub>1</sub> | 0      | 1 |  |  |

| S <sub>0</sub><br>S <sub>1</sub> | S <sub>0</sub><br>S <sub>2</sub><br>S <sub>3</sub><br>S <sub>0</sub> | $S_2$          | 1      | 1 |  |  |

| $S_2$                            | $S_3$                                                                | $S_3$          | 1      | 1 |  |  |

| $S_2$<br>$S_3$                   | S <sub>0</sub>                                                       | S <sub>0</sub> | 1      | 1 |  |  |

Shift 4 times after St is activated

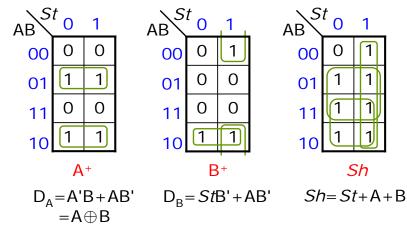

#### Serial Adder with Accumulator Control Circuit Design

Derivation of control circuit equations

#### Transition table

|                                  | AB | A+B+          |    |  |  |

|----------------------------------|----|---------------|----|--|--|

|                                  |    | <i>St</i> = 0 | 1  |  |  |

| S <sub>0</sub>                   | 00 | 00            | 01 |  |  |

| $S_1$                            | 01 | 10            | 10 |  |  |

| $S_2$                            | 10 | 11            | 11 |  |  |

| $S_0$<br>$S_1$<br>$S_2$<br>$S_3$ | 11 | 00            | 00 |  |  |

|                                  | D  |               |    |  |  |

| State Assignment                 |    |               |    |  |  |

7

St 0

0

1

1

1

1

1

1

1

Sh

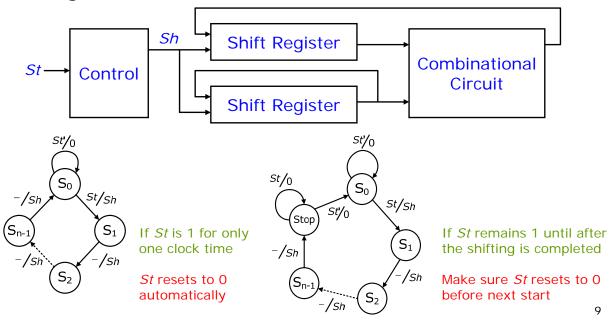

### Serial Adder with Accumulator Typical Serial Processing Unit

Typical serial processing unit with n-bit shift registers

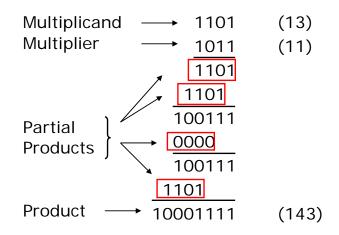

### Design of a Parallel Multiplier

- Design a parallel adder for positive binary numbers

- Require only shifting and adding

- Add two binary numbers at a time

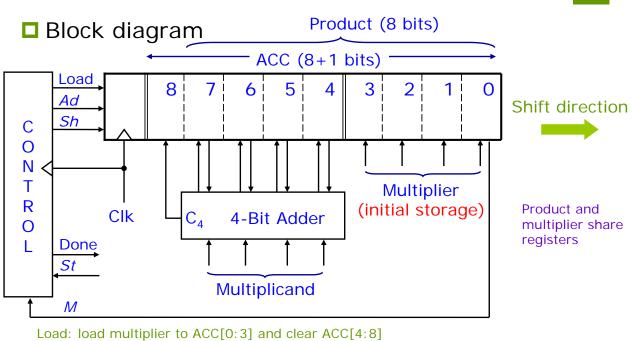

### Design of a Parallel Multiplier Parallel Binary Multiplier

Load: load multiplier to ACC[0:3] and clear ACC[4:8] Ad: add signal (to store adder outputs in ACC[4:7] and C<sub>4</sub> in ACC[8]) Sh: shift the ACC contents one place to the right M: current multiplier bit

### Design of a Parallel Multiplier Parallel Binary Multiplier

| Operation example                    | {product, multiplier}                   |  |  |  |  |

|--------------------------------------|-----------------------------------------|--|--|--|--|

| initial contents of product register | 0 0 0 0 0 1 0 1 <mark>1 ←</mark> M (11) |  |  |  |  |

| (add multiplicand because M = 1)     | 1101 (13)                               |  |  |  |  |

| after addition                       | 011011011                               |  |  |  |  |

| after shift                          | 0 0 1 1 0 1 1 0 <b>1</b> ←M             |  |  |  |  |

| (add multiplicand because M = 1)     | 1101                                    |  |  |  |  |

| after addition                       | 100111101                               |  |  |  |  |

| after shift                          | 0 1 0 0 1 1 1 1 <mark>0 ←</mark> M      |  |  |  |  |

| (skip addition because $M = 0$ )     |                                         |  |  |  |  |

| after shift                          | 0 0 1 0 0 1 1 1 1 <b>① ←</b> M          |  |  |  |  |

| (add multiplicand because $M = 1$ )  | 1101                                    |  |  |  |  |

| after addition                       | 100011111                               |  |  |  |  |

| after shift (final answer)           | 010001111 (143)                         |  |  |  |  |

Dividing line between product and multiplier

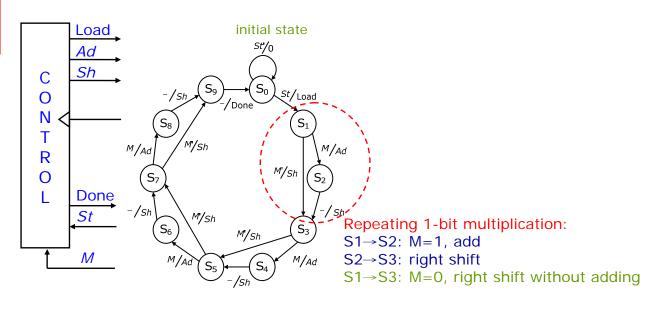

#### Design of a Parallel Multiplier Control Circuit Design

#### Method 1 (direct implementation)

13

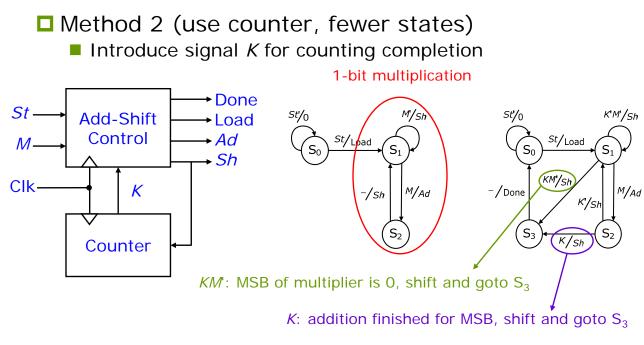

### Design of a Parallel Multiplier Control Circuit Design

How many states in total (including add-shift control and counter)?

# Design of a Parallel Multiplier Control Circuit Design

#### Method 2 (cont'd)

#### Operation example for 1101×1011

| Time           | State                 | Counter | Product<br>Register | St | М | К | Load | Ad | Sh | Done |

|----------------|-----------------------|---------|---------------------|----|---|---|------|----|----|------|

| t <sub>o</sub> | S <sub>0</sub>        | 00      | 000000000           | 0  | 0 | 0 | 0    | 0  | 0  | 0    |

| t <sub>1</sub> | S <sub>0</sub>        | 00      | 00000000            | 1  | 0 | 0 | 1    | 0  | 0  | 0    |

| t <sub>2</sub> | S <sub>1</sub>        | 00      | 000001011           | 0  | 1 | 0 | 0    | 1  | 0  | 0    |

| t <sub>3</sub> | $S_2$                 | 00      | 011011011           | 0  | 1 | 0 | 0    | 0  | 1  | 0    |

| t <sub>4</sub> | S <sub>1</sub>        | 01      | 001101101           | 0  | 1 | 0 | 0    | 1  | 0  | 0    |

| t <sub>5</sub> | <b>S</b> <sub>2</sub> | 01      | 100111101           | 0  | 1 | 0 | 0    | 0  | 1  | 0    |

| t <sub>6</sub> | S <sub>1</sub>        | 10      | 010011110           | 0  | 0 | 0 | 0    | 0  | 1  | 0    |

| t <sub>7</sub> | S <sub>1</sub>        | 11      | 001001111           | 0  | 1 | 1 | 0    | 1  | 0  | 0    |

| t <sub>8</sub> | <b>S</b> <sub>2</sub> | 11      | 100011111           | 0  | 1 | 1 | 0    | 0  | 1  | 0    |

| t <sub>9</sub> | $S_3$                 | 00      | 010001111           | 0  | 1 | 0 | 0    | 0  | 0  | 1    |

|                |                       |         |                     |    |   |   |      |    |    |      |