# **CHAPTER 15 CMOS DIGITAL LOGIC CIRCUITS**

## **Chapter Outline**

- 15.1 CMOS Logic-Gate Circuits

- 15.2 Digital Logic Inverters

- 15.3 The CMOS Inverter

- 15.4 Dynamic Operation of the CMOS Inverter

- 15.5 Transistor Sizing

- 15.6 Power Dissipation

# **15.1 CMOS Logic-Gate Circuits**

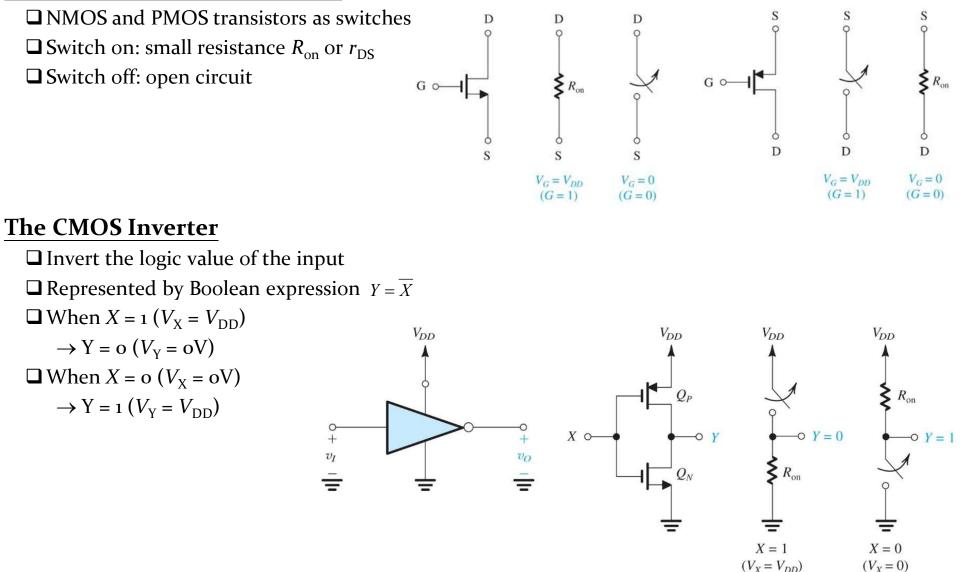

## **Switch-Level Transistor Model**

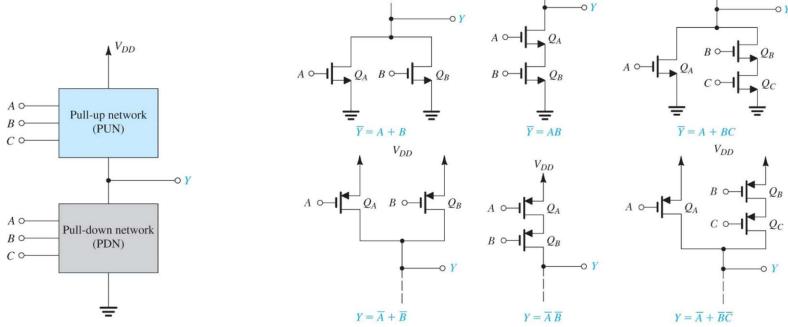

## **General Structure of CMOS Logic**

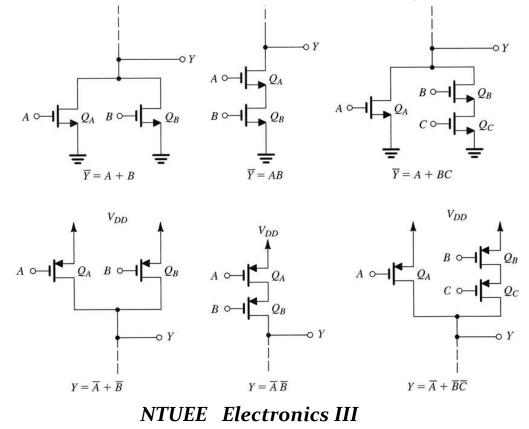

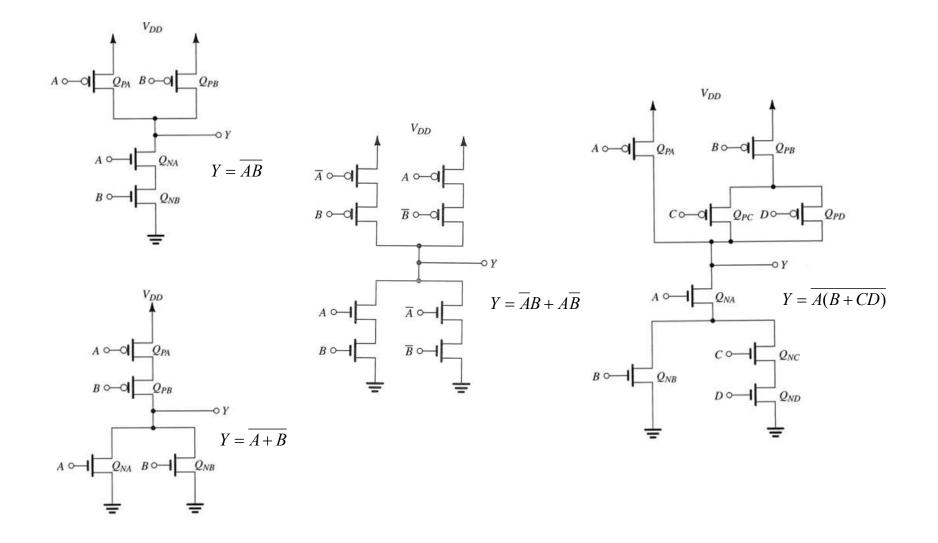

NMOS pull-down network (PDN) and PMOS pull-up network (PUN) operated by input variables in a complementary fashion

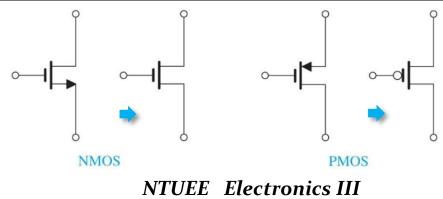

### Alternative Circuit Symbols for MOSFETS in Digital Circuits

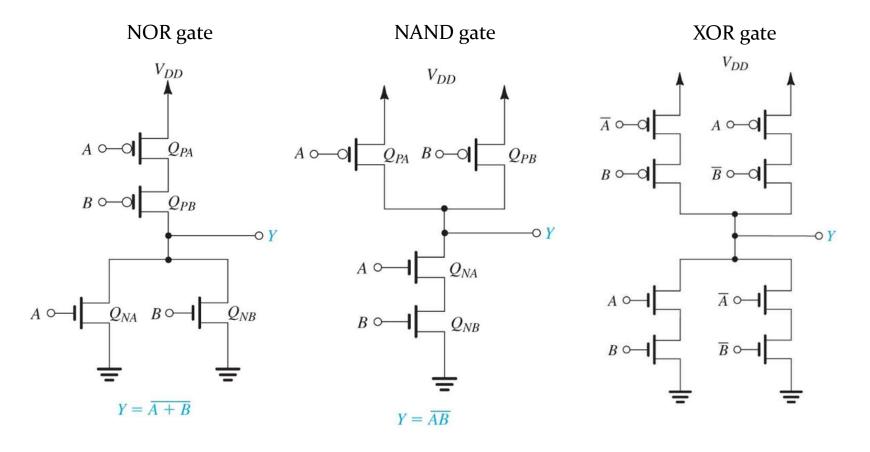

### **Two-Input Logic Gates**

□ Two-input NOR gate, two-input NAND gate and Exclusive-OR gate

## **Synthesis Method for PUN and PDN**

- □ The PDN can be directly synthesized by expressing the **inverted** Boolean function in **uncomplemented** variables (inverters are needed if complemented variables appear in the expression)

- □ The PUN can be directly synthesized by expressing the **nonverted** Boolean function in **complemente**d variables (inverters are needed if uncomplemented variables appear in the expression)

- The PUN can be also obtained from the PDN (and vice versa) using the duality property

## **Examples for CMOS Logic Gates**

# 15.2 Digital Logic Inverters

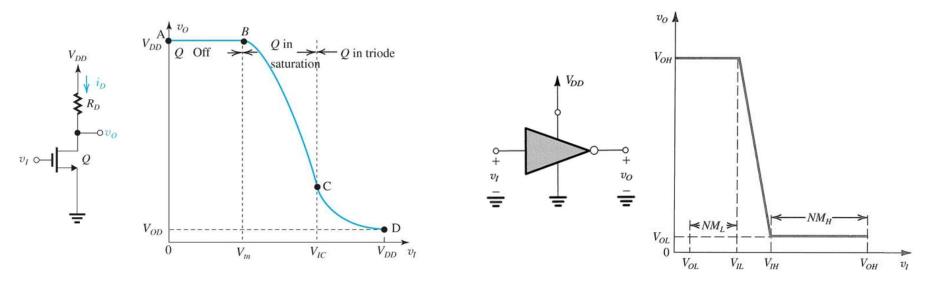

## The Voltage-Transfer Characteristic (VTC)

□ The function of the inverter is to invert the logic value of its input signal

□ The voltage-transfer characteristic is used to evaluate the quality of inverter operation

#### □ VTC parameters

- $V_{OH}$ : output high level

- $V_{OL}$ : output low level

- $V_{\text{IH}}$ : the minimum value of input interpreted by the inverter as a logic 1

- $V_{\rm IL}$ : the maximum value of input interpreted by the inverter as a logic o

- **Transition region: input level between**  $V_{\rm IL}$  and  $V_{\rm IH}$

### **Noise Margins**

□ The VTC is generally non-linear

$\Box$  V<sub>IH</sub> and V<sub>IL</sub> are defined as the points at which the slope of the VTC is -1

$\Box$  Robustness (noise margin at a high level):  $NM_{\rm H} = V_{\rm OH} - V_{\rm IH}$

$\Box$  Robustness (noise margin at a low level):  $NM_{\rm L} = V_{\rm IL} - V_{\rm OL}$

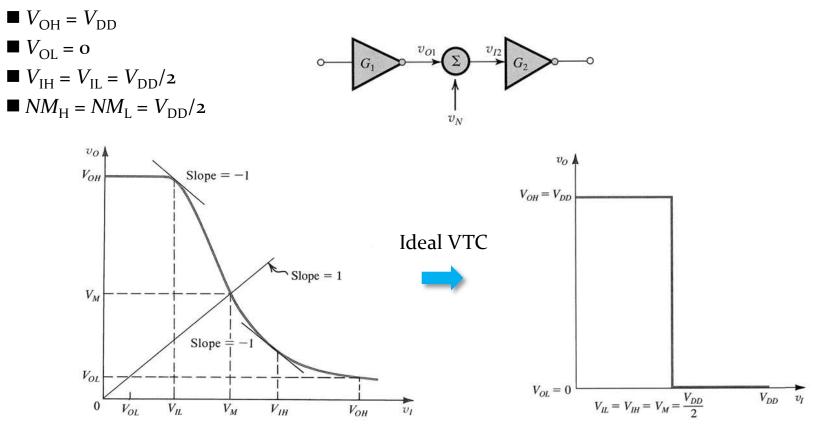

□ Static inverter characteristics for ideal VTC:

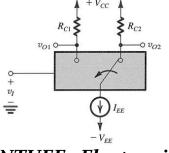

NTUEE Electronics III

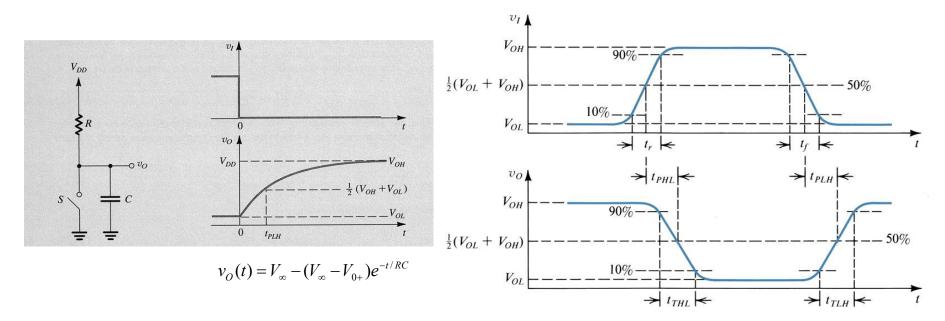

## **Propagation Delay**

- $\Box t_{PHL}$  : high-to-low propagation delay

- $\Box t_{PLH}$  : low-to-high propagation delay

- $\Box t_{\rm P}$  (propagation delay) =  $(t_{\rm PLH}+t_{\rm PHL})/2$

- $\Box$  Maximum switching frequency  $f_{\text{max}} = 1/2t_{\text{P}}$

□ The output transient of the inverter can be characterized by a *RC* charge/discharge model

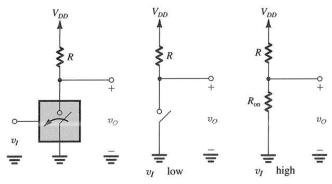

### **Inverter Implementation**

□ Simplest implementation of the inverter with a MOSFET and a load

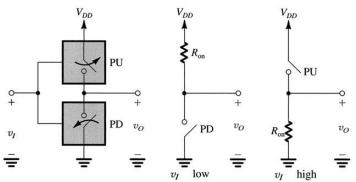

□ Inverter implementation with complementary switches

□ Inverter implementation with a double-throw switch

**NTUEE** Electronics III

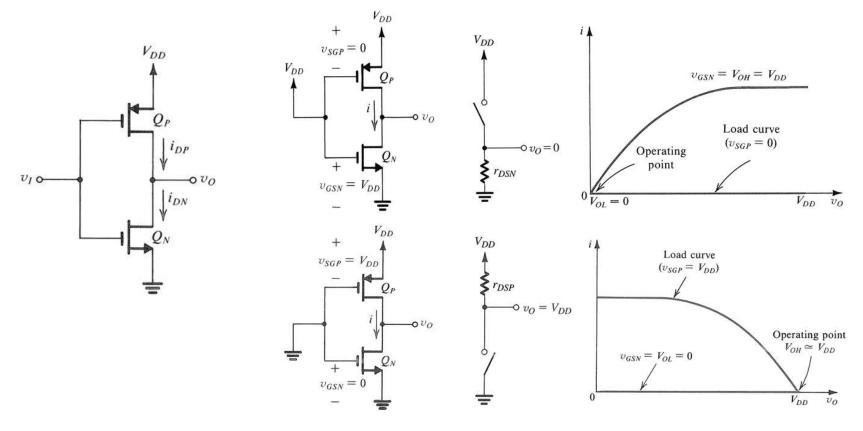

## 15.3 The CMOS Inverter

## **Circuit Operation**

- A CMOS inverter consists of an n-channel and a p-channel MOSFET

- The n-channel device turns on and the p-channel device turns off as the input level goes high

- □ The p-channel device turns on and the n-channel device turns off as the input level goes low

□ The turn-on device is modeled by a resistance:  $r_{DSN} = [k_n (W/L)_n (V_{DD} - V_{in})]^{-1}$  and  $r_{DSP} = [k_p (W/L)_p (V_{DD} - |V_{ip}|)]^{-1}$ □  $V_{OH} = V_{DD}$  and  $V_{OL} = 0$  for any CMOS inverter

NTUEE Electronics III

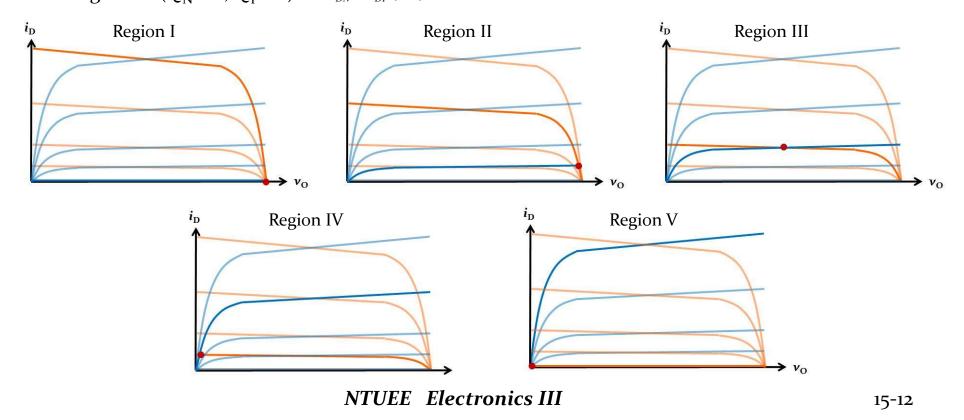

$\Box$  The transistors go through five different operation regions as the input goes from o to  $V_{\text{DD}}$

Region I:

$$(Q_{N} \text{ off; } Q_{P} \text{ tri.})$$

$$i_{DN}(=0) = i_{DP}$$

Region II:  $(Q_{N} \text{ sat.; } Q_{P} \text{ tri.})$

$$i_{DN} = \frac{1}{2}k_{n}(v_{I} - V_{in})^{2} = i_{DP} = k_{p}\left[(V_{DD} - v_{I} - |V_{ip}|)(V_{DD} - v_{O}) - \frac{1}{2}(V_{DD} - v_{O})^{2}\right]$$

Region III:  $(Q_{N} \text{ sat; } Q_{P} \text{ sat})$

$$i_{DN} = \frac{1}{2}k_{n}(v_{I} - V_{in})^{2} = i_{DP} = \frac{1}{2}k_{p}(V_{DD} - v_{I} - |V_{ip}|)^{2}$$

Region IV:  $(Q_{N} \text{ tri.; } Q_{P} \text{ sat.})$

$$i_{DN} = k_{n}\left[(v_{I} - V_{in})v_{O} - \frac{1}{2}v_{O}^{2}\right] = i_{DP} = \frac{1}{2}k_{p}(V_{DD} - v_{I} - |V_{ip}|)^{2}$$

Region V:  $(Q_{N} \text{ tri.; } O_{P} \text{ off})$

$$i_{DN} = i_{DP}(=0)$$

### Static Characteristics of the CMOS Inverter

$\Box$  Ratioless logic:  $V_{OH}$  and  $V_{OL}$  are independent of ratio of the transistors

$$V_{\rm OH} = V_{\rm DD}$$

$$\mathbf{V}_{OL} = \mathbf{0}$$

□ Static power dissipation is zero for both states

□ Noise margins can be determined by the VTC

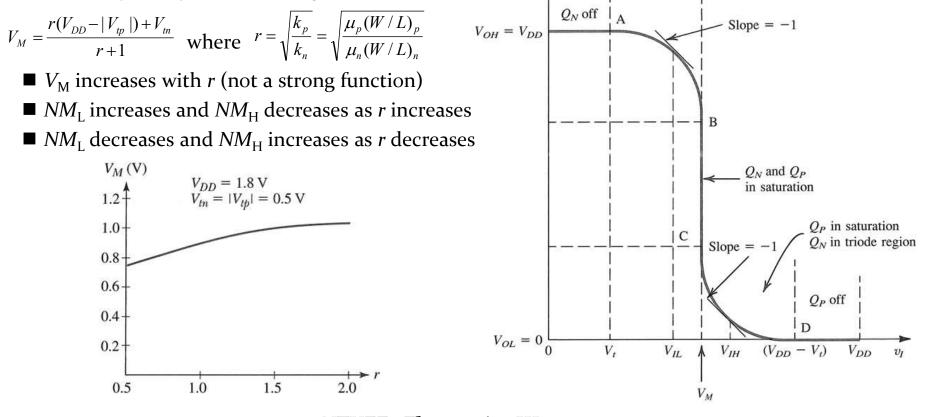

$\Box$  The switching voltage (when  $v_{I} = v_{O}$ ) is defined by

$Q_N$  in saturation

Vol

$O_P$  in triode region

NTUEE Electronics III

15-13

#### The Matched Inverter

□ A matched inverter has equivalent pull-up and pull-down device with  $k_n = k_p$  and  $V_{tn} = |V_{tp}| = V_t$ □ The VTC is symmetric

$\Box$  Determine  $V_{\text{IL}}$  from the VTC in Region II:

$$\frac{1}{2}(v_{I} - V_{t})^{2} = \left[ (V_{DD} - v_{I} - V_{t})(V_{DD} - v_{O}) - \frac{1}{2}(V_{DD} - v_{O})^{2} \right]$$

$$v_{I} - V_{t} = -(V_{DD} - v_{O}) - (V_{DD} - v_{I} - V_{t})\frac{dv_{O}}{dv_{I}} + (V_{DD} - v_{O})\frac{dv_{O}}{dv_{I}}$$

$$V_{IL} = \frac{1}{9}(3V_{DD} + 2V_{t})$$

$\Box$  Determine  $V_{\rm IH}$  from the VTC in Region IV:

$$(v_{I} - V_{t})v_{o} - \frac{1}{2}v_{o}^{2} = \frac{1}{2}(V_{DD} - v_{I} - V_{t})^{2}$$

$$v_{o} + (v_{I} - V_{t})\frac{dv_{o}}{dv_{I}} - v_{o}\frac{dv_{o}}{dv_{I}} = -(V_{DD} - v_{I} - V_{t})$$

$$V_{IH} = \frac{1}{8}(5V_{DD} - 2V_{t})$$

□ Noise margins:  $NM_{\rm H} = NM_{\rm L} = ({}_{3}V_{\rm DD} + {}_{2}V_{\rm t})/8$ □ Switching voltage:  $V_{\rm M} = V_{\rm DD}/2$

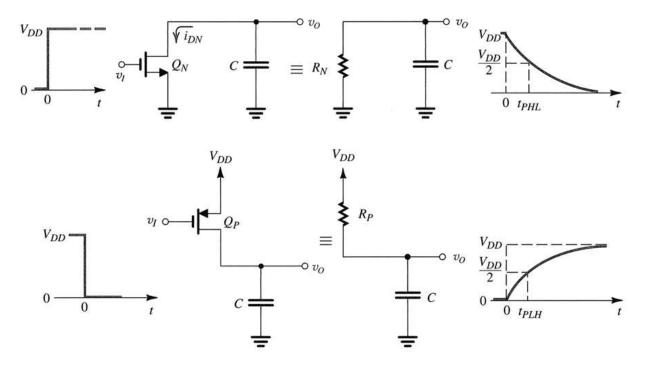

# 15.4 Dynamic Operation of the CMOS Inverter

### **Determining the Propagation Delay**

$\Box$  Evaluated by charging/discharge the output capacitor C through  $Q_{\rm P}$  and  $Q_{\rm N}$

- Average current method:  $V_{DD}$ UII  $\blacksquare t_{\rm PHL}$ :  $V_{DD}$  $I_{av} = \frac{1}{2} [i_{DN}(E) + i_{DN}(M)]$  $i_{DN}(E) = \frac{1}{2}k_n(V_{DD} - V_{tn})^2$ VIO  $\downarrow^{i_{DN}}$ 1<sub>PHL</sub>  $\leftarrow t_{PLH}$  $V_{DD}$  $i_{DN}(M) = k_n \left[ (V_{DD} - V_{in}) \left( \frac{V_{DD}}{2} \right) - \frac{1}{2} \left( \frac{V_{DD}}{2} \right)^2 \right]$  $V_{DD}$  $t_{PHL} = \frac{CV_{DD}}{2I_{m}} = \frac{\alpha_n C}{k_n V_{DD}}$ Operating where  $\alpha_n = 2 / \left[ \frac{7}{4} - \frac{3V_{tn}}{V_{DD}} + \frac{V_{tn}^2}{V_{DD}^2} \right]$ IDN A point at t = 0 + $v_{GSN} = V_{DD}$  $V_{DD}$ E  $\blacksquare t_{\rm PLH}$ : IDN Capacitor discharge  $t_{PLH} = \frac{CV_{DD}}{2I_{av}} = \frac{\alpha_p C}{k_p V_{DD}}$ through  $Q_N$ Operating point Operating where  $\alpha_p = 2 \left[ \frac{7}{4} - \frac{3 |V_{tp}|}{V_{DD}} + \frac{V_{tp}^2}{V_{DD}^2} \right]$ after switching point at is completed t = 0 -D  $\frac{V_{DD}}{2}$ VDD vo  $(V_{DD} - V_t)$

- Propagation delay:  $t_{\rm P} = (t_{\rm PHL} + t_{\rm PLH})/2$

□ An alternative approach:

- Modeling the turn-on device as a resistance

- Use RC charge/discharge behavior to evaluate the propagation delay

- The empirical values of the resistors are given by

$$R_N = \frac{12.5}{(W/L)_n} (k\Omega)$$

and  $R_P = \frac{30}{(W/L)_p} (k\Omega)$

- $t_{\text{PHL}}$  = 0.69 $R_{\text{N}}C$  and  $t_{\text{PLH}}$  = 0.69 $R_{\text{P}}C$

- Step function at input may underestimate propagation delay  $\rightarrow t_{PHL} \cong R_N C$  and  $t_{PLH} \cong R_P C$

NTUEE Electronics III

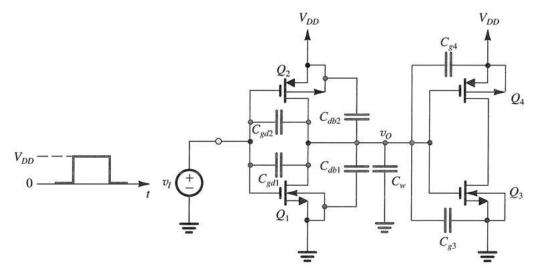

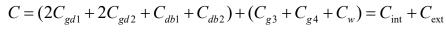

## **Determining the Equivalent Load Capacitance**

- □ Components accountable for the equivalent load capacitance

- Transistor parasitic capacitances from  $Q_1$  and  $Q_2$  (intrinsic component)

- Input capacitance of the following stages (extrinsic component)

- Wiring capacitance or interconnect capacitance (extrinsic component)

NTUEE Electronics III

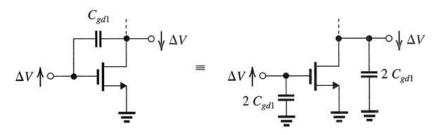

# 15.5 Transistor Sizing

## **Inverter Sizing**

□ Minimum length permitted by the technology is usually used as the length for all channels

$\Box$  Device aspect ratio  $(W/L)_n$  is usually selected in the range 1 to 1.5

$\Box$  The selection of  $(W/L)_p$  is relative to  $(W/L)_n$

• Matched inverter by  $(W/L)_p : (W/L)_n = \mu_n : \mu_p$

$\blacksquare$   $(W/L)_p = (W/L)_n$ : minimum area, small propagation delay

■  $(W/L)_p = 2(W/L)_n$ : a frequently used compromise

$\Box$  Transistor sizing (aspect ratios are increased by a factor of *S*) versus propagation delay

• Load capacitance:  $C = C_{int} + C_{ext} = SC_{int0} + C_{ext}$

Equivalent resistance:

$$R_{eq} = \frac{1}{2} \left( \frac{R_N}{S} + \frac{R_P}{S} \right) = \frac{R_{eq0}}{S}$$

Propagation delay:  $t_P = 0.69 \left( \frac{R_{eq0}}{S} \right) (SC_{int0} + C_{ext}) = 0.69 \left( R_{eq0}C_{int0} + \frac{1}{S}R_{eq0}C_{ext} \right)$

$\Box$  The propagation decreases as *S* increases for cases where *C*<sub>ext</sub> dominates

$\Box$  The propagation is nearly independent of the transistor sizing (*S*) for cases where  $C_{int}$  dominates

## **Effects of Fan-In and Fan-Out**

Each additional input to a CMOS gate requires two additional transistors

□ Increases the chip area and the propagation delay due to excess capacitive loading

The number of NAND gate is typically limited to 4

□ Redesign the logic design may be required for a higher number of inputs

Advantages of using CMOS logic: static power dissipation, ratioless design, noise margin

Disadvantage of using CMOS logic: area, complexity, capacitive loading, propagation delay

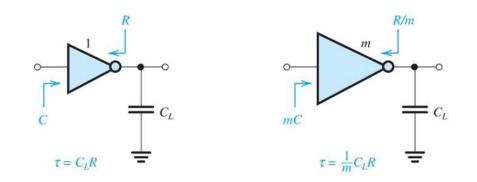

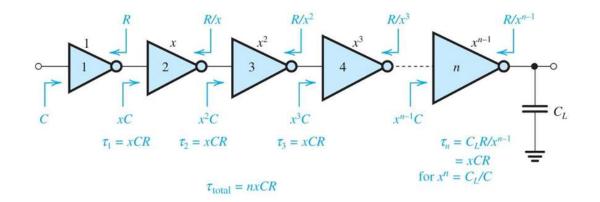

### **Driving a Large Capacitance**

- □ A large capacitive load drastically increases the propagation delay

- □ Use a large inverter to drive the load could alleviate the propagation delay

- □ The input capacitance increases accordingly equivalently shifting the burden forward

- □ Chain of scaled inverters in cascade to alleviate the problem with large capacitive load

# 15. 6 Power Dissipation

### **Power Dissipation**

□ Static power dissipation: power dissipated when the inverter stays in logic 0 or logic 1

Dynamic power dissipation: power dissipated as the output is switching

•  $0.5C(V_{DD})^2$  is dissipated in the PUN in each cycle

•  $0.5C(V_{DD})^2$  is dissipated in the PDN in each cycle

• Dynamic power dissipation:  $P_D = f C(V_{DD})^2$

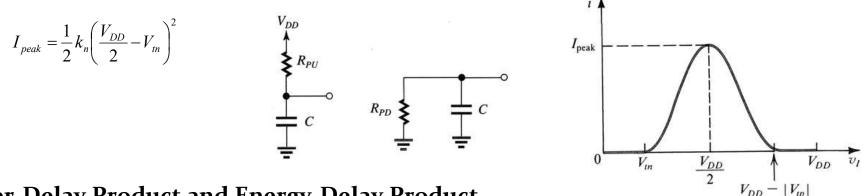

□ Another component of power dissipation during switching results from the current conduction through  $Q_P$  and  $Q_N$  and the peak current for a matched inverter is given by

### **Power-Delay Product and Energy-Delay Product**

□ Power and delay are often in conflict for inverter operation

□ Power-delay product is a figure-of-merit for comparing logic-circuit technologies or families

**D** Power-delay product is defined as  $PDP = P_D t_P = CV_{DD}^2 / 2$

$\Box$  Energy-delay product (energy per transition) is defined as  $EDP = CV_{DD}^2 t_P / 2$