# **Topic IV**

# **Verification Techniques Overview (II)**

Static Analysis, Physical Verification & Testing

系統晶片驗證 SoC Verification

Sep, 2004

# What we will cover in this topic...

- ◆ Static analysis

- Linting

- Clock domain checking

- Static timing analysis

- Signal Integrity

- ◆Physical verification

- DRC

- LVS

- Design for Manufacturability (DfM)

- **♦**Testing

SoC Verification

Prof. Chung-Yang (Ric) Huang

# Vhat is Linting? 字典首頁 > 字典瀏覽 > lint 釋 義 排 析 lint [Int] n. (名詞 noun) n. (名詞 noun) 1. [物] (亞麻布經刮絨後的軟麻布(舊時用作繃帶) 2. [物] 棉絨飛花 3. [物] [美] 皮棉 4. [物] [蘇格蘭] (作為植物織維的)亞麻 ▲ top Source: Yahoo! 奇摩字典 Soc Verification Prof. Chung-Yang (Ric) Huang 3

# **The Origin of Linting**

- ◆Named after the Unix programming tool lint

- Picks fluff/lint out of your programming code.

- Seeks out common errors, missing attributes, poor formatting that may be technically correct

SoC Verification

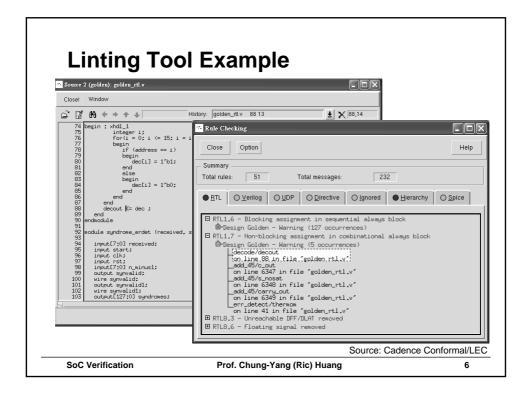

#### **HDL Linting**

- ◆ Also called "RTL Design Rule Checking"

- ◆ Gives warnings/errors to:

- Bad/ambiguous coding styles

- Potential simulation/synthesis inconsistency

- ◆ Tool support

- Special linting tools

- Synthesis tools

- Simulation/Verification tools

- It's a good practice to pay attention to the linting errors, however ---

(Problem) User may ignore the warnings/errors because there are usually too many...

SoC Verification

Prof. Chung-Yang (Ric) Huang

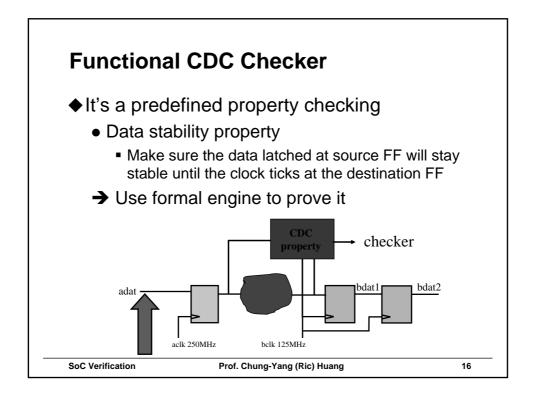

# **Linting vs. Super Linting**

- **♦**Linting

- Structural, syntactical, semantics checking

- **♦** Super linting

- Structural + functional, predefined property checking

- Properties are automatically extracted during the RTL compilation process

- Need to call formal verification engine

**SoC Verification**

Prof. Chung-Yang (Ric) Huang

7

# **Super Linting Properties**

- ◆ Also called "predefined properties", "static properties", etc.

- Examples

- Bus contention (one-hot checks)

- Design don't-care

- Synopsys full/parallel case

- X assignment

- Array bound check (e.g. assign a[y] = data; )

- Finite State Machine (FSM) checks

- State reachability

- State transition

- Dead lock checks

- Register racing condition

- Branch enabling condition

- Floating point error

SoC Verification

Prof. Chung-Yang (Ric) Huang

# What we will cover in this topic...

- ◆ Static analysis

- Linting

- Clock domain checking

- Static timing analysis

- Signal Integrity

- ◆Physical verification

- DRC

- LVS

- Design for Manufacturability (DfM)

- **◆**Testing

SoC Verification

Prof. Chung-Yang (Ric) Huang

۵

#### What is Clock Domain?

- ◆Clock domain

- Signals that share the same clock (tree) source (i.e. have the synchronized timing)

Modern designs usually have multiple clocks with very high frequencies

SoC Verification

Prof. Chung-Yang (Ric) Huang

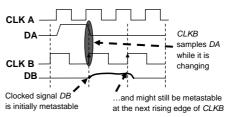

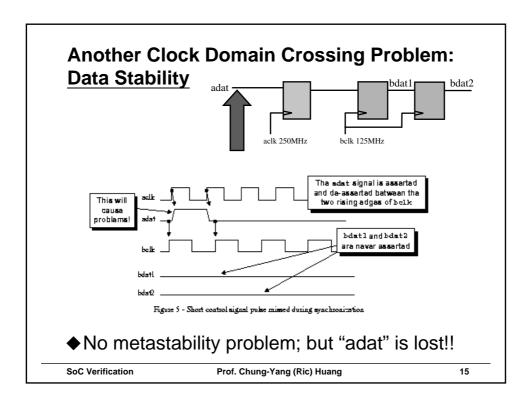

# **Clock Domain Crossing Problem**

What's the problem??

◆ Signals crossing asynchronous domains create metastability

Source: Cadence Design Systems

SoC Verification

Prof. Chung-Yang (Ric) Huang

11

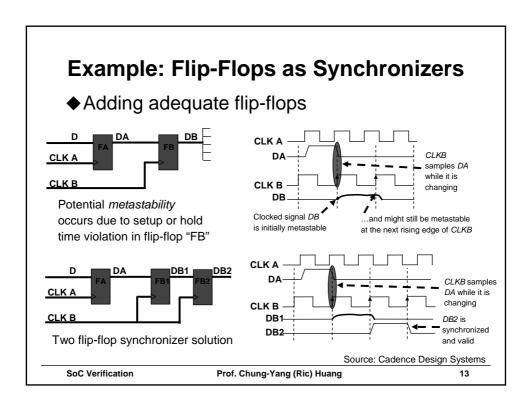

# **Handling Asynchronous Crossings**

- Using synchronizers

- Metastable signals need time to settle to a stable value

- By adding synchronizers, the metastable signal can have additional clock cycles to become stable

- ◆Synchronizer examples:

- Flip-Flops

- Mux

- Multi-cycle path

SoC Verification

Prof. Chung-Yang (Ric) Huang

#### **Clock Domain Crossing Checks**

- However, given a multi-million-gate design, which may have <u>billions or trillions of paths</u>, how do you make sure you have properly added in synchronizers and have no domain crossing problems?

- → Finding Synchronization errors could be very expensive by STA or simulation

- → Clock Domain Checker (CDC) performs a structural check and can find clock domain crossing violations more quickly

SoC Verification

Prof. Chung-Yang (Ric) Huang

# In short,

- Linting and clock domain checking allow you to identify potential RTL design problems up front

- Structural checks are very fast

- Functional checks are mostly local, and thus usually can work for large designs too

- → can be integrated into design flow easily

SoC Verification

Prof. Chung-Yang (Ric) Huang

17

# What we will cover in this topic...

- ◆ Static analysis

- Linting

- Clock domain checking

- Static timing analysis

- Signal Integrity

- ◆Physical verification

- DRC

- LVS

- Design for Manufacturability (DfM)

- **♦**Testing

SoC Verification

Prof. Chung-Yang (Ric) Huang

# How fast can your design run?

- Depend on the critical delay of your circuit

- Max clock frequency = 1 / (critical delay)

- Timing (delay) paths of your circuit

- Combinational paths (i.e. no FFs). 4 types:

- 1. Register to register

- 2. PI to register

- 3. Register to PO

- 4. PI to PO

- Critical delay path

- The timing path that has the longest delay

SoC Verification

Prof. Chung-Yang (Ric) Huang

19

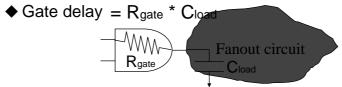

# How to calculate the delay?

R \* C = (d V / d I) \* (d Q / d V) = d T

◆ R & C (and sometimes Inductance) are extracted from layout netlist

SoC Verification

Prof. Chung-Yang (Ric) Huang

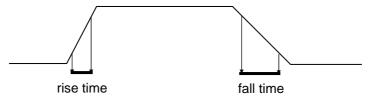

# **Delay Calculation**

- ◆ Delay is pattern dependent

- rise time != fall time (aka. setup time != hold time)

- ◆ Delay also depends on

- Process

- Voltage

- Temperature

- → Linear or Table-Lookup model

SoC Verification

Prof. Chung-Yang (Ric) Huang

21

# **Issues about Delay Calculation**

- ◆In deep submicron, wire delay > gate delay

- Need physical (placement & routing) information

- ◆Since delay is pattern dependent

- Given a path, different input patterns will result in different delays

- → (Dynamic) Timing analysis is very expensive!!

SoC Verification

Prof. Chung-Yang (Ric) Huang

# **Static Timing Analysis (STA)**

- ◆For each node (gate or wire) in a circuit, compute its ---

- (Best, worst) x (rise time, fall time)

- ◆ Perform topological traversals

- Propagate forward the arrival time

- Compute backward the required time

- Create the slack (i.e. required arrival time) graph and obtain the critical delay path(s)

SoC Verification

Prof. Chung-Yang (Ric) Huang

23

# **Advantages of Static Timing Analysis**

- ◆ Exhaustive timing analysis

- ♦No input vectors required

- ◆Much more efficient than dynamic methods

- Faster operations

- Capacity of millions of gates

Source: CIC course

SoC Verification

Prof. Chung-Yang (Ric) Huang

#### **Disadvantages of Static Timing Analysis**

- ◆For synchronous logic only

- ◆Much more setup efforts

- ◆Tricky constraints needed for design that is NOT single-clock flip-flop-based

- Multiple clocks

- False paths

- Latches

- Multi-cycle paths

- ◆Lack of consistent conventions

Source: CIC course

SoC Verification

Prof. Chung-Yang (Ric) Huang

٥.

# Do you see a niche market?

SoC Verification

Prof. Chung-Yang (Ric) Huang

# What we will cover in this topic...

- ◆ Static analysis

- Linting

- Clock domain checking

- Static timing analysis

- Signal Integrity

- ◆Physical verification

- DRC

- LVS

- Design for Manufacturability (DfM)

- **◆**Testing

SoC Verification

Prof. Chung-Yang (Ric) Huang

27

# **Signal and Design Integrity Problem**

- ◆ As processes shrink and frequencies increase

- → signal integrity problems created by 2<sup>nd</sup> order physical effects

- i.e. Capacitance coupling, capacitance + inductance

- Signal integrity problems

- Cross talk induced functional errors

- Cross talk induced timing violations

- Power (IR) drop or Ground bounce

- Design integrity problems (discussed later)

- Electromigration

- Hot electron effects

- Wire self-heating

Source: Cadence S&DI White Paper

SoC Verification

Prof. Chung-Yang (Ric) Huang

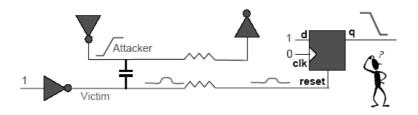

#### **Cross Talk Induced Functional Errors**

Coupling noise can cause functional failures.

- ◆ Two wires are very close to each other

- ◆ Attacker (aggressor) wire switching affects the victim wire

Source: Cadence CeltIC

SoC Verification

Prof. Chung-Yang (Ric) Huang

29

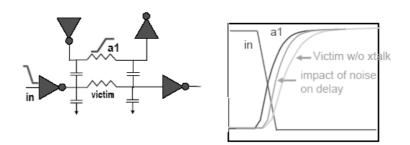

#### **Cross Talk Induced Hold Time Violations**

- ◆ Helpful glitch: a fast transition on a aggressor net that switches in the same direction as a victim net

- ◆ Helpful glitch causes a victim net to transition faster

- → hold time violation

Source: Cadence CeltIC

SoC Verification

Prof. Chung-Yang (Ric) Huang

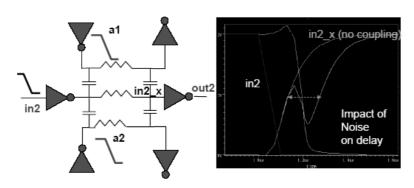

#### **Cross Talk Induced Setup Time Violations**

- ◆ Unhelpful glitch: a fast transition on a aggressor net that switches in the opposite direction from a victim net

- ◆ Unhelpful glitch causes a victim net to transition slower

- → setup time violation

Source: Cadence CeltIC

SoC Verification

Prof. Chung-Yang (Ric) Huang

31

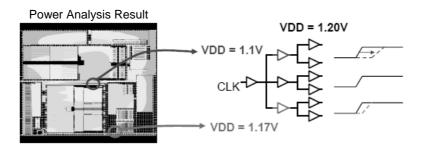

# Voltage (IR) Drop or Ground Bounce Problems

- ◆The fact

- The wires from chip input power pin(s) to power nodes (Vdd) circuitry inside have resistance

- → The voltage that goes to internal circuitry is less than that applied to the chip

- ◆The problems

- The circuit may not get enough voltage and can malfunction or not meet the timing specifications

SoC Verification

Prof. Chung-Yang (Ric) Huang

# **Voltage Drop Impacts on Timing**

- ◆ IR Drop (ground bounce) increases clock skew

- → Hold time violations

- ◆ IR Drop (ground bounce) increases signal skew

- → Setup time violations

Source: Cadence VoltageStorm

SoC Verification

Prof. Chung-Yang (Ric) Huang

33

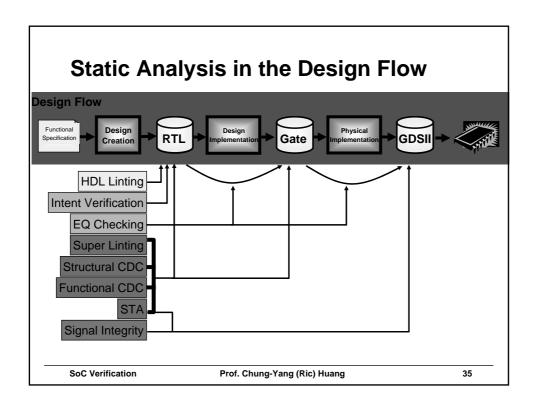

# **Signal Integrity Problem Prevention and Correction**

- Needs to take cross-coupling effects and peak voltage drops into consideration

- Different Tools' Approaches

- 1. Post-layout SI analysis

- 2. Combined STA and SI approaches

- Integrated physical implementation and analysis engine

SoC Verification

Prof. Chung-Yang (Ric) Huang

# What we will cover in this topic...

- ◆ Static analysis

- Linting

- Clock domain checking

- Static timing analysis

- Signal Integrity

- ◆Physical verification

- DRC

- LVS

- Design for Manufacturability (DfM)

- **◆**Testing

SoC Verification

Prof. Chung-Yang (Ric) Huang

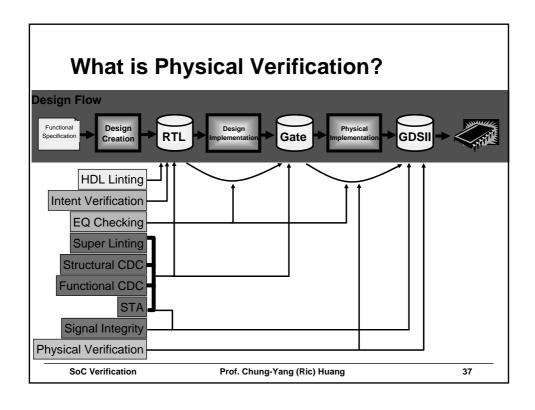

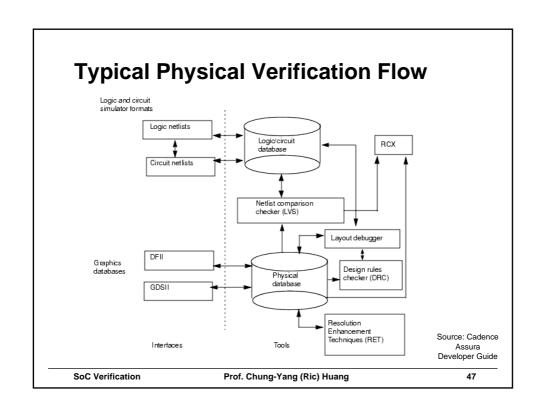

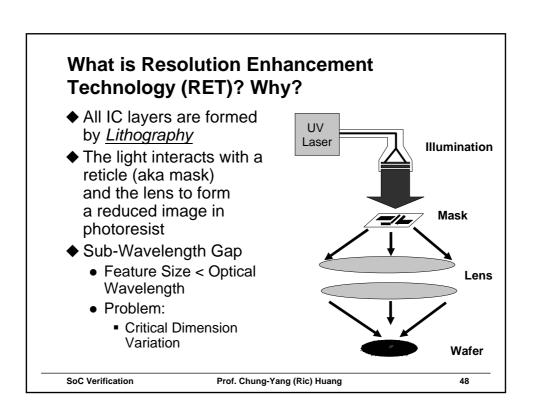

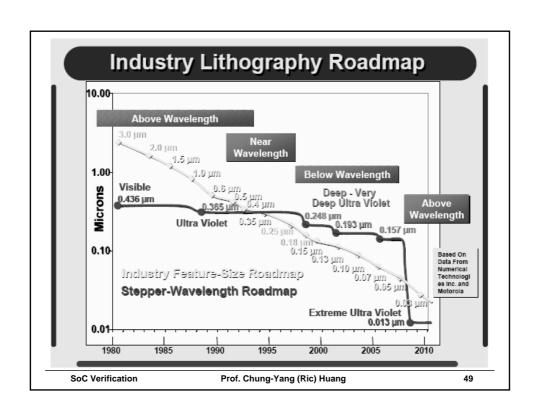

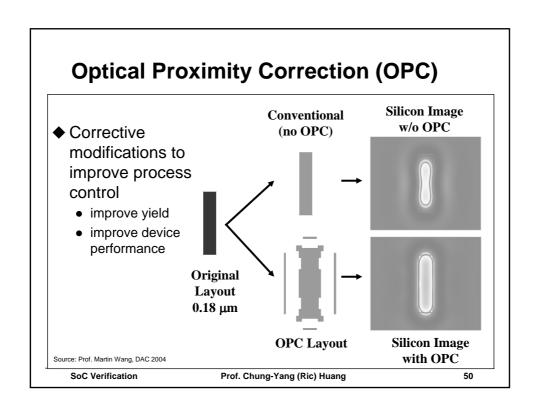

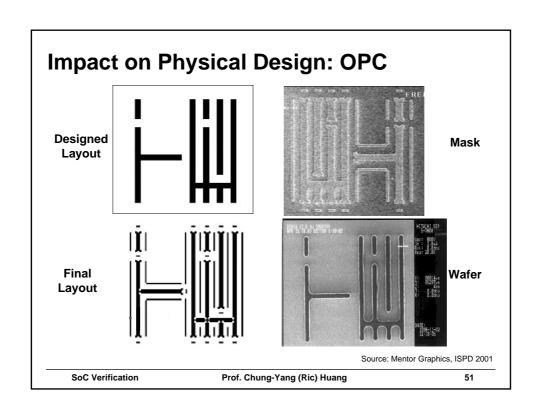

# **Types of Physical Verification**

- ◆ Design Rule Check (DRC)

- Layout Versus Schematic (LVS)

- ◆ Resolution Enhancement Technology (RET)

- Optical Proximity Correction (OPC) (or Optical and Process Correction)

- Phase-Shifting Mask (PSM)

- Others

- Electrical Rule Check

- Device-level Resistance, Capacitance, Induction Extraction

SoC Verification

Prof. Chung-Yang (Ric) Huang

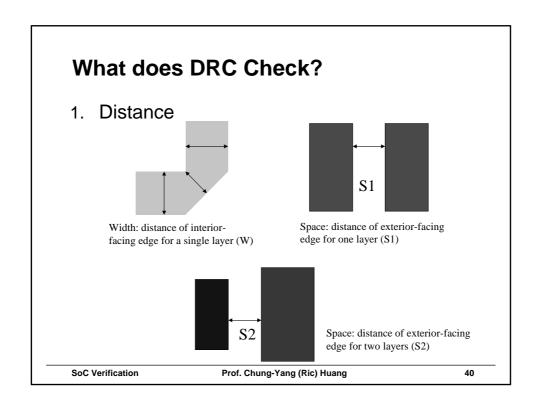

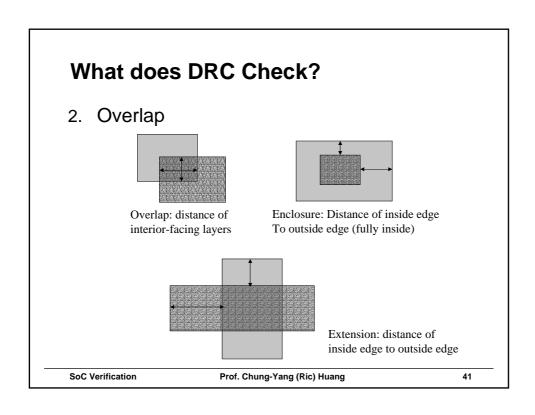

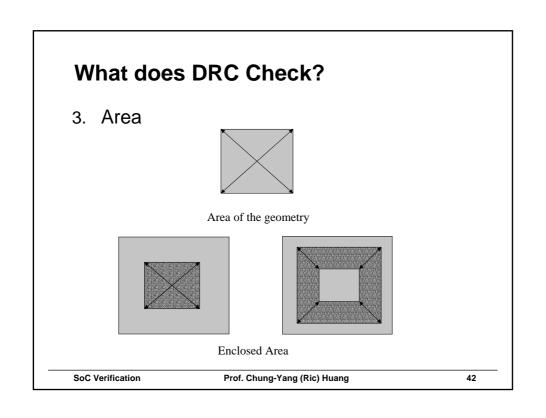

# **Design Rule Check (DRC)**

- ◆ Check if a *physical implementation* is in conformance with a given *IC manufacturing process*

- Inputs:

- Layout file --- geometrical shapes (e.g. GDS-II)

- IC manufacturing rule document (e.g. TSMC 0.18um Mixed Signal (1P6M) CMOS)

- Outputs:

- Layout geometrical violations that may affect

- 1. Manufacturability

- 2. Yield of the chip

- [Note] Don't confused with HDL Design Rule Checking

SoC Verification

Prof. Chung-Yang (Ric) Huang

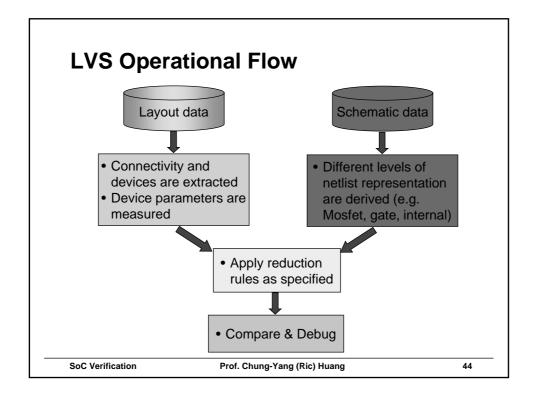

# **Layout Versus Schematic (LVS)**

- ◆Compare the connectivity of <u>a physical</u>

<u>layout</u> design to the <u>schematic</u> from which it was designed (e.g. Spice, Verilog)

- Perform design matching of nets, devices, and device parameters

- In addition, even Layout vs Layout (LVL), or Schematic vs Schematic (SVS) can be checked

SoC Verification

Prof. Chung-Yang (Ric) Huang

#### **LVS Rules Files**

[Using Cadence Assura as example]

- ◆ extract.rul

- Contains rules for defining and extracting devices and nets from the layout data

- compare.rul

- Contains rules for comparing the schematic netlist to the extracted layout netlist

- binding.rul

- Optional binding rules to help Assura LVS match the schematic to layout

- ◆ deviceinfo.rul

- A support file that can be used to import a schematic netlist

Source: Cadence Assura Developer Guide

SoC Verification

Prof. Chung-Yang (Ric) Huang

45

#### LVS vs. Functional Equivalence Checking

- **◆LVS**

- Structurally compare layout and schematic netlists

- ◆Functional Equivalence Checking

- Can ompare netlists from RTL to GDS-II (layout)

- Use formal engine for functional comparison

- For layout circuit, need to extract logic functions from transistor netlist

SoC Verification

Prof. Chung-Yang (Ric) Huang

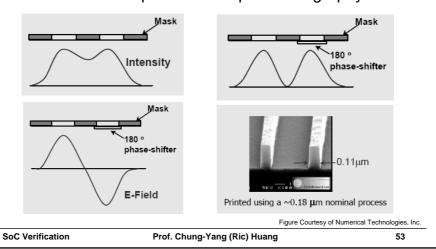

# **Phase Shifting Mask (PSM)**

◆ Uses phase-modulation at the mask level to further the resolution capabilities of optical lithography

# **Advantages of PSM**

- ◆ Smaller feature sizes

- ◆Improved yield (process latitude)

- Dramatically extends useful life of current equipment

- ◆Performance Boost

- Chip Area/Cost Advantage for Embedded Systems

- Modified Architecture Based on Higher Speed Busses

Source: Motorola

SoC Verification

Prof. Chung-Yang (Ric) Huang

# What we will cover in this topic...

- ◆ Static analysis

- Linting

- Clock domain checking

- Static timing analysis

- Signal Integrity

- ◆Physical verification

- DRC

- LVS

- Design for Manufacturability (DfM)

- **◆**Testing

SoC Verification

Prof. Chung-Yang (Ric) Huang

# **Manufacturing Defects**

- ◆ Defects in chip manufacturing will lead to failure silicon or severe reliability problems

- ◆ Defects occur at

- Front end of the line (FEOL), i.e., devices

- Back end of the line (BEOL), i.e., interconnect and vias

- BEOL defects are increasingly dominant

- ◆Main BEOL failure mode: spot defects

SoC Verification

Prof. Chung-Yang (Ric) Huang

57

# **Spot Defect Classification**

- Intra-layer extra material

- → short-circuit faults

- Intra-layer missing material

- → open circuit faults

- Inter-layer extra material

- → open faults (blocked vias)

- Inter-layer missing material

- → short-circuit faults (oxide pinholes)

Source: Fujitsu Labs

SoC Verification

Prof. Chung-Yang (Ric) Huang

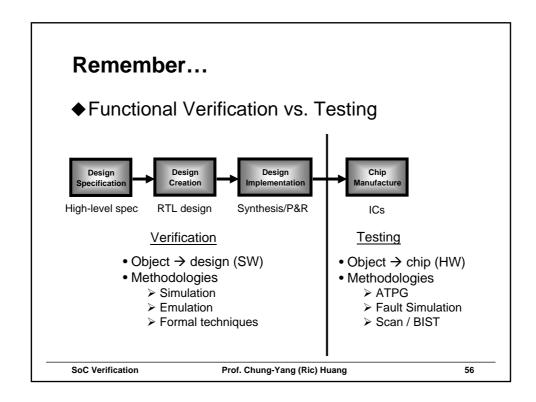

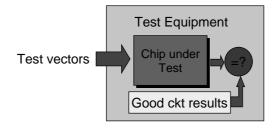

# Testing is ---

◆Apply test vectors on real chip and check if there is any unexpected result or the chip becomes malfunctioned

SoC Verification

Prof. Chung-Yang (Ric) Huang

59

#### **Test Vector (Pattern) Generation**

- ◆Methods

- Random

- Automatic (Deterministic) Test Pattern Generation (ATPG)

- ◆Goal: to generate quality test vectors that can detect as many defects as possible

- → Need a quantitative metric to measure the quality of tests

SoC Verification

Prof. Chung-Yang (Ric) Huang

#### **Test Measurement**

- ◆ How good is your test?

- ◆ Fault model

- To characterize defects (faults) into different categories

- Short / Open faults

- → For each node in the circuit, it has either short or open fault

- → Cover > 90% common defects

- → Correspond to stuck-at-1 / stuck-at-0 faults

- → With fault model, defects can then be enumerated and test quality can then be measured

- ◆ Fault coverage

- (#detected faults) / (# total faults)

**SoC Verification**

Prof. Chung-Yang (Ric) Huang

61

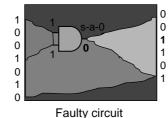

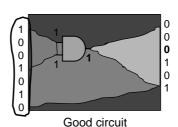

#### For a test vector to detect a fault...

- It must generate different responses at the fault location for the good and faulty circuits

- 2. The above difference must be propagated to primary outputs for observation

SoC Verification

Prof. Chung-Yang (Ric) Huang

#### **Automatic Test Pattern Generation (ATPG)**

- Given a fault list, generate as few vectors and detect as many faults as possible

- Usually use stuck-at-1/0 (s-a-0/1) fault model

- Assume single-fault model

- Branch-and-bound algorithms

- (Details to cover later)

SoC Verification

Prof. Chung-Yang (Ric) Huang

63

#### Remember ---

- ◆ For a test vector to detect a fault...

- 1. It must generate different responses at the fault location for the good and faulty circuits

- → Controllability problem

- 2. The above difference must be propagated to primary outputs for observation

- → Observability problem

- Registers are neither controllable nor observable in a chip

- → Sequential ATPG is very difficult (rarely used)

- ◆ Use <u>combinational ATPG + DfT</u> techniques

SoC Verification

Prof. Chung-Yang (Ric) Huang

# **Design for Testability (DfT) Techniques**

- ◆Scan Design

- Add a "scan chain" on registers in order to "scan in" test vectors and "scan out" simulation results

- Scan and functional modes

- **◆**Test Point Insertions

- Insert circuitry in critical internal points of the circuit to increase controllability or observability

SoC Verification

Prof. Chung-Yang (Ric) Huang

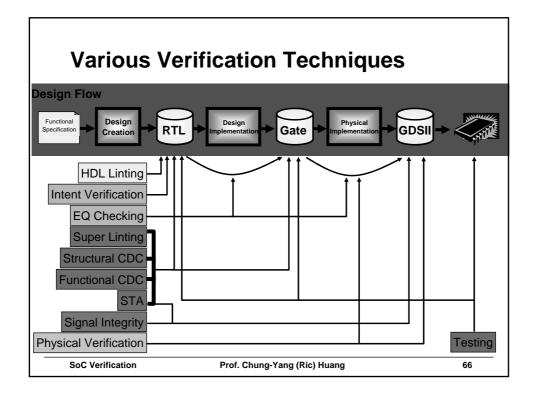

# What we have learned about various verification techniques

- Simulation

- ◆ Emulation / hardware acceleration / rapid prototyping

- ◆ Formal verification

- · Property checking

- Equivalence checking

- Static analysis

- Linting

- · Clock domain checking

- · Static timing analysis

- Signal Integrity

- Physical verification

- DRC

- LVS

- Design for Manufacturability (DfM)

- Testing

SoC Verification

Prof. Chung-Yang (Ric) Huang

67

- What types of verification techniques have you used?

- What kinds of new verification techniques will be useful for your next design?

- How efficient is your current verification practice?

- ◆Do you expect any new verification techniques? In what area?

SoC Verification

Prof. Chung-Yang (Ric) Huang