### **Topic VI**

## System Level Design and Verification

系統晶片驗證 SoC Verification

Sep, 2004

### What we will cover in this topic...

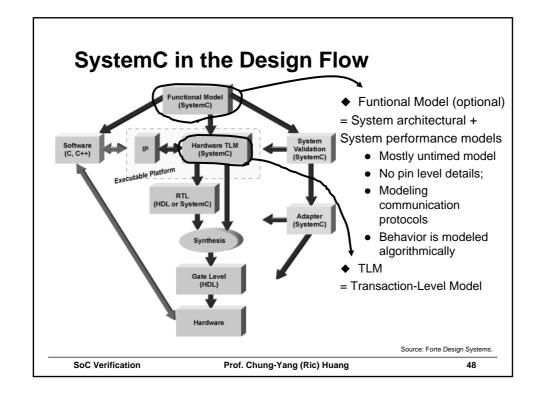

- ◆What is system-level design, and why?

- ◆SystemC basics

- ◆Transaction-Level Modeling (TLM)

- ◆System or unit-level verification

- ◆SystemC verification library

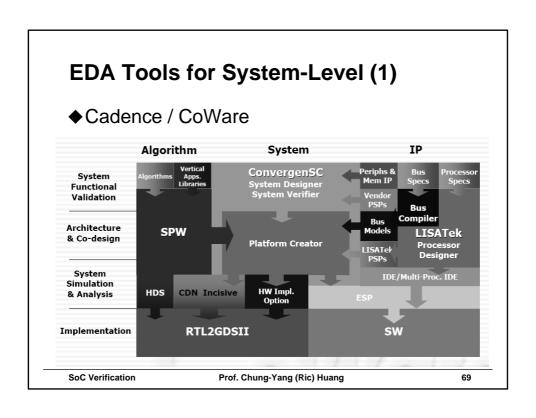

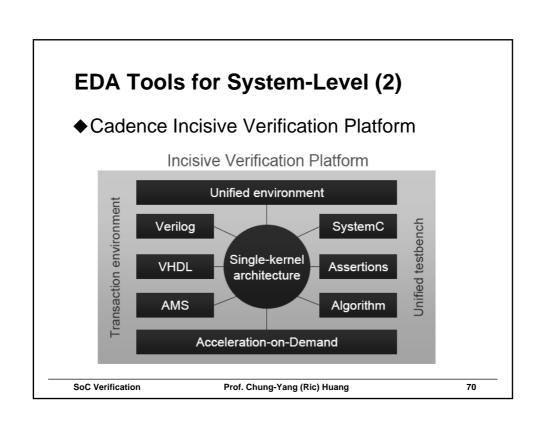

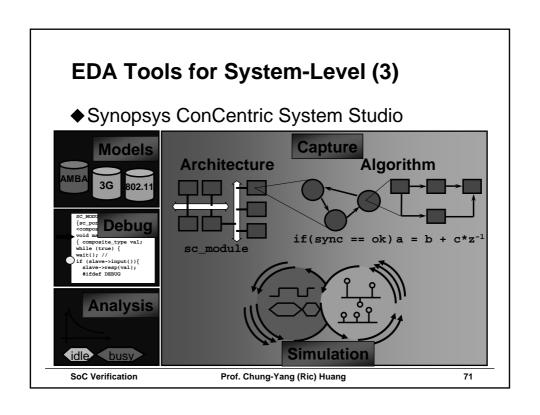

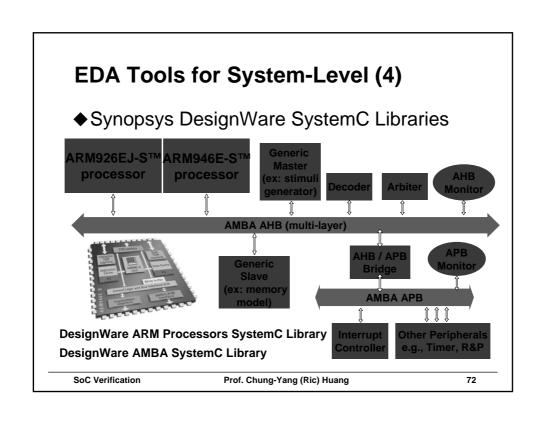

- ◆EDA Tools for System-Level

SoC Verification

Prof. Chung-Yang (Ric) Huang

### What is System-Level Design?

- Designing a circuit from a system-level point of view

- What is the formal (unambiguous) sense of the system specification and requirement?

- What kind of architectures (CPU, OS, bus, etc) are we going to use?

- Is this a valuable/feasible product (in terms of performance, project span, ROI, etc)?

SoC Verification

Prof. Chung-Yang (Ric) Huang

3

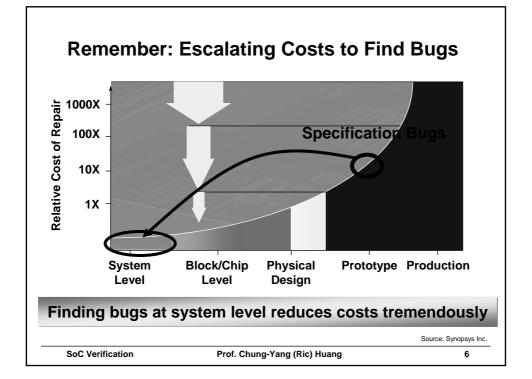

### Why System-Level Design?

(we have designed systems already...)

Because we need system-level analysis and verification!!

SoC Verification

Prof. Chung-Yang (Ric) Huang

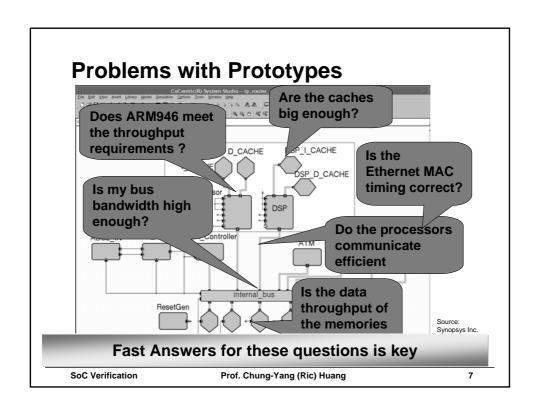

### **Old-Style System Design**

- System requirements are translated and partitioned into specs on various design blocks (by system/chip architect)

- Each HW/SW designer designs on his/her own block(s)

- System is integrated after all the block designs are done

- Usually use prototype for integrated system validation

- Why cannot we do better?

- Deficiency in automatic system design environment

- HW/SW co-design /co-verification environment

- Tool supports

- Design languages

- Organization problem

- Chip architect vs. designer vs. verification engineer

- ◆ Any problem?

- Inaccurate (lack of system analysis)

- Conservative (because of inaccuracy...)

- · Limited system design flexibility

SoC Verification

Prof. Chung-Yang (Ric) Huang

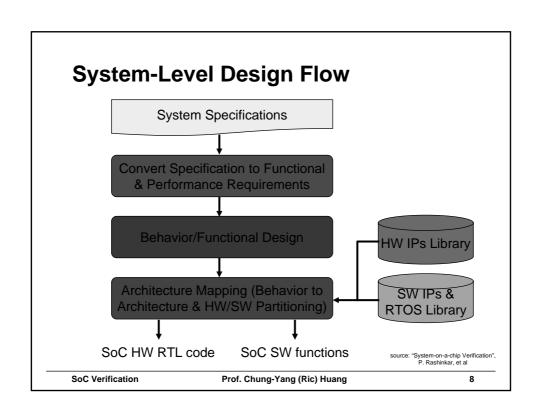

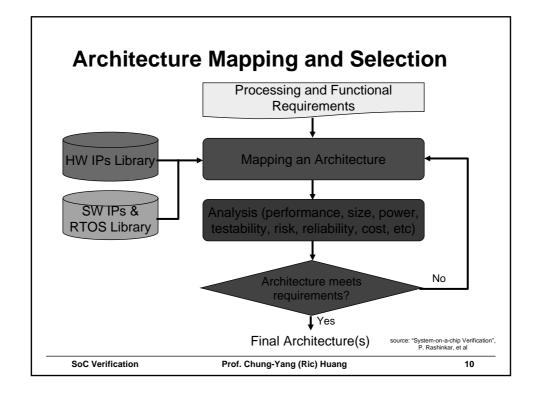

### **Behavior and Functional Design**

- ◆ Goal

- Be able to formalize the criteria to select the architecture and HW/SW partitioning

- Algorithms are analyzed to assess the processing/computational, memory, and I/O requirements

- What kinds of architecture are you going to use?

- Can they satisfy the system specifications?

- → Algorithm and process flows are translated to data and control flows that are independent of architecture

SoC Verification

Prof. Chung-Yang (Ric) Huang

### But how?

What kind of languages and tools do we use for system-level design?

**SoC Verification**

Prof. Chung-Yang (Ric) Huang

11

### **SystemC**

A System-Level

Design and Verification

Language

SoC Verification

Prof. Chung-Yang (Ric) Huang

### **SystemC History**

- ◆ Pre-release: Synopsys, Frontier Design and CoWare

- Using C++ for modeling hardware and software components of a system

- ♦ Ver. 0.9: Sep 1999

- Ownership → Open SystemC Initiative (OSCI)

- ♦ Ver. 1.0: Jan 2000

- Introduced a set of macros for easier reading and writing

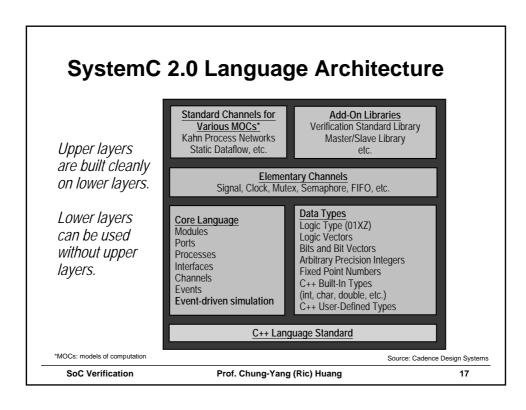

- ♦ Ver 2.0: July 2001

- Changed SystemC from a cycle based to event based simulator

- Added user-defined interfaces, channels and ports

- Restructured the core language

- ◆ SystemC Verification Library (SCV Library): Oct 2002

- Transaction-based verification

- Randomization

- Constraint Solver

- ◆ Ver 3.0: ??

- · Focus on software and scheduler modeling

Source: Forte Design Systems. & Cadence Design Systems

SoC Verification

Prof. Chung-Yang (Ric) Huang

13

### Why C++ is not enough?

|                       | C++                              | SystemC                                                           |

|-----------------------|----------------------------------|-------------------------------------------------------------------|

| Notion of time        | No                               | Introduced and implemented                                        |

| Concurrency           | No                               | Processes defined;<br>executed in parallel<br>within simulators   |

| Hardware<br>data type | Inadequate<br>(e.g. Tri-state Z) | Arbitrary precision integers, fixed point numbers, 4-valued logic |

Source: Forte Design Systems

SoC Verification Prof. Chung-Yang (Ric) Huang

14

### **Facts about SystemC**

- ◆A bridge between HW and SW designs

- ◆Open source C++ library with event-driven simulator

- "Extends" the C++ language without changing the syntax by using classes

- Can use regular C++ development environment

- Modules are introduced as a means of encapsulating behavior and describing hierarchy

SoC Verification

Prof. Chung-Yang (Ric) Huang

15

### **SystemC Development Environment** your standard C/C++ development environment compiler linker debugger class library source files for system and simulation kernel and test benches "make" "executable specification a.out he free GNU tools library can be can be used for executable = simulator compilation and the OSCI website (www.systemc.org Source: Forte Design Systems **SoC Verification** 16 Prof. Chung-Yang (Ric) Huang

### What we will cover for SystemC...

- ◆ Modeling structures

- Module

- Port

- ◆Communication structures

- Interface

- Channel

- Port

- Events and Processes

- ◆Other items…

SoC Verification

Prof. Chung-Yang (Ric) Huang

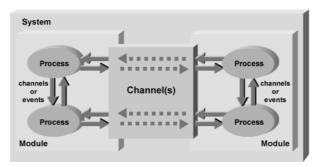

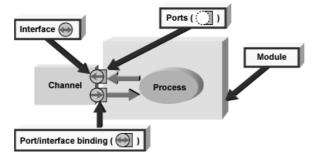

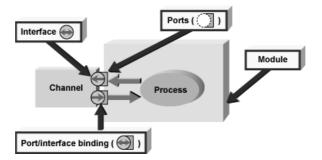

### A SystemC System

- 1. A SystemC system consists of a set of modules

- 2. Modules contain concurrent processes; they are used to create hierarchy

- 3. Processes describe functionality and communicate with each other through channels or events

- 4. Inter-Module communication is through channels

Source: Forte Design Systems

SoC Verification

SoC Verification

Prof. Chung-Yang (Ric) Huang

19

20

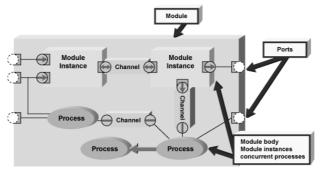

# SystemC Hierarchy Instance names By the property of the prop

Prof. Chung-Yang (Ric) Huang

### **Basic Modeling Structure**

- ◆ Module: may represent a system, a block, a board, a chip...etc

- Ports: represent the interface, pins etc., depending upon what the module represents

- Module instances at a peer level are connected through their ports with a channel

- 2. Parent to child connection of module instances is done port to port

- 3. Processes communicate through channels or events

Source: Forte Design Systems.

SoC Verification

Prof. Chung-Yang (Ric) Huang

21

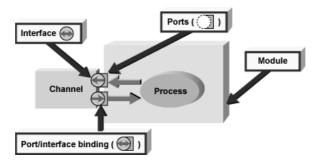

### **Three Basic Communication Structures**

- 1. Interface

- 2. Channel

- 3. Port

SoC Verification

Prof. Chung-Yang (Ric) Huang

### **Basic Communication Structures (1/3)**

### Interface

- ◆ Provides a set of method declarations, but no implementations and no data fields

- To define sets of methods that channels must implement.

- ◆ Ports are connected to channels through interfaces

- A port sees only those channel methods that are defined by the interface

- → Not able to access any other method or data field in the channel

- ◆ SystemC 2.0 allows users to define their own interfaces.

Source: Forte Design Systems && OSCI "Functional Spec 2.0"

SoC Verification

Prof. Chung-Yang (Ric) Huang

22

### **Interface Examples**

SoC Verification

Prof. Chung-Yang (Ric) Huang

### Interface Examples (cont'd)

```

//

template <class T>

class sc_read_write_if

: public sc_read_if<T>,

public sc_write_if<T>

{};

```

SoC Verification

Prof. Chung-Yang (Ric) Huang

25

### **Basic Communication Structures (2/3)**

### Channel

- ◆ Implements one or more interface's methods

- ◆ The container for communication functionality

- ◆ Not necessarily a point-to-point connection; may be connected to more than two modules.

Source: Forte Design Systems && OSCI "Functional Spec 2.0"

SoC Verification

Prof. Chung-Yang (Ric) Huang

### **Two Types of Channels**

- 1. Primitive channels

- No visible structure, they contain no processes and cannot directly access other channels. Examples of primitive channels in SystemC are:

- sc\_signal<T>

- sc\_signal\_rv<N>

- sc\_fifo<T>

- sc\_mutex

- sc\_semaphore

- sc buffer<T>

- 2. Hierarchical channels

- Have structure

- Similar to modules in they can have processes, ports and instances of other channels or modules

- Can directly access other channels

Source: Forte Design Systems

SoC Verification

Prof. Chung-Yang (Ric) Huang

27

### Primitive Channel Example: sc\_signal<T>

- ◆Implements the sc\_signal\_inout\_if interface

- Used to describe hardware signals and are typically used in RTL modeling

- ◆Signals are unresolved

- May only have one writer, but may have multiple readers

- If more than one process writes to a signal an error occurs

Source: Forte Design Systems

SoC Verification

Prof. Chung-Yang (Ric) Huang

# sc\_signal<T> ◆ Syntax sc\_signal<T> signal\_name, signal\_name, ...; ◆ Example of syntax: SC\_MODULE (module\_name) { sc\_signal<int> d; sc\_signal<char> e; sc\_signal<sc\_int<10> > f; // rest of module not shown };

### Example use of methods of sc\_signal<T>

Prof. Chung-Yang (Ric) Huang

```

// declarations

sc_signal<int> sig_a; // channel used inside module

int a;

// use

a = sig_a.read(); // read local channel

sig_a.write(5); // write local channel

// read() and write() are event methods of sc_signal

```

Source: Forte Design Systems

SoC Verification

SoC Verification

Prof. Chung-Yang (Ric) Huang

30

### **Another Primitive Channel Example**

### // main.cpp

```

int sc_main(int argc, char **argv) {

sc_fifo<int> fifo_chan(5); // fifo channel of depth 5

// module instantiations

source src("src");

sink snk("snk");

// connect src & snk

src.output(fifo_chan);

snk.input(fifo_chan);

sc_start();

}

```

Source: Forte Design Systems

SoC Verification

Prof. Chung-Yang (Ric) Huang

31

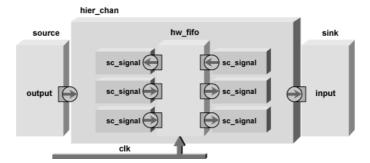

### **Change It to Hierarchical Channel**

- The same source and sink modules as in the previous example

- As an adapter which "translates" between the interfaces for the hw\_fifo and the source and sink modules

- ◆ The module hw\_fifo implements a FIFO

Source: Forte Design Systems.

SoC Verification

Prof. Chung-Yang (Ric) Huang

### **Basic Communication Structures (3/3)**

### Port

- Created from the base class sc\_port and bound to an interface type

- ◆ Syntax

- sc\_port<interface\_type, N> port\_name, port\_name,...;

- N is the number of channels that can be connected to the port

Source: Forte Design Systems

SoC Verification

Prof. Chung-Yang (Ric) Huang

33

### **Port Example**

```

SC_MODULE(my_module) {

// port in_p with 2 channels connected

sc_port<sc_signal_in_if<int>,2> in_p;

sc_port<sc_signal_inout_if<int> > out_p;

// body of module

};

```

Source: Forte Design Systems

SoC Verification

Prof. Chung-Yang (Ric) Huang

## What is modules in SystemC?

**SoC Verification**

Prof. Chung-Yang (Ric) Huang

35

### **Modules in SystemC**

- A module is a container

- ◆ It is similar to a Verilog "module" or a VHDL "entity."

- Each module is described using a header file (module\_name.h) and an implementation file (module\_name.cpp)

- ♦ Modules contain

- Ports

- Internal channel variables

- Internal data variables

- · Processes of different types

- Other methods

- Instances of other modules

- Constructor

Source: Forte Design Systems

SoC Verification

Prof. Chung-Yang (Ric) Huang

### **Syntax of Module**

◆ Syntax:

```

SC_MODULE ( module_name) {

// body of module

};

```

- SC\_MODULE is a macro for: struct module\_name : public sc\_module

- A module inherits from the base class sc\_module defined in the SystemC library

- ◆SC\_CTOR is a macro for constructor

Source: Forte Design Systems

SoC Verification

Prof. Chung-Yang (Ric) Huang

37

### What we will cover for SystemC...

- ◆ Modeling structures

- Module

- Port

- ◆Communication structures

- Interface

- Channel

- Port

- ◆Events and Processes

- ◆Other items...

SoC Verification

Prof. Chung-Yang (Ric) Huang

### **Events in SystemC**

- ◆ Basic synchronization object

- Used to synchronize between processes

- Declared inside a module

- ◆ Syntax:

```

sc_event event_name, event_name,...;

```

◆ Example :

```

SC_MODULE(ex) {

// Ports not shown

// events

sc_event ev_1, ev_2;

// Rest of the module not shown

};

```

Source: Forte Design Systems

SoC Verification

Prof. Chung-Yang (Ric) Huang

39

### **Processes in SystemC**

- Describes functionality

- ◆ Do not call processes directly in the code

- → Invoked by the kernel based on either its static or dynamic sensitivity lists

- Not hierarchical can not have a process inside another process

- ◆ Use channels or events to communicate with each other

- Registered inside the constructor of the module class

- Types

- Methods (SC\_METHOD)

- Threads (SC\_THREAD)

- Clocked Threads (SC\_CTHREAD)

Source: Forte Design Systems

SoC Verification

Prof. Chung-Yang (Ric) Huang

### **Process Creation (1/4)**

1. Declaration

```

// code in header file my_module.h

SC_MODULE(my_module){

// ports

sc_fifo_in<int> a;

sc_fifo_in<bool> b;

sc_fifo_out<int> x;

sc_fifo_out<int> y;

// Internal channels

sc_fifo<bool>c;

sc_fifo<int> d;

// Method Process

void my_method_proc(); // function prototype

. . .

};

```

Source: Forte Design Systems

SoC Verification

Prof. Chung-Yang (Ric) Huang

41

### **Process Creation (2/4)**

2. Definition

```

// The recommended style is to put the

// definition in a separate implementation file:

// module_name.cpp

void my_module :: my_method_proc(){

x = a + d;

y = b / c;

}

```

Source: Forte Design Systems

SoC Verification

Prof. Chung-Yang (Ric) Huang

### **Process Creation (3/4)**

3. Registration (in module constructor) SC\_CTOR(my\_module) {

// register method process

SC\_METHOD(my\_method\_proc);

// rest of constructor not shown

. . .

}

Source: Forte Design Systems

SoC Verification

Prof. Chung-Yang (Ric) Huang

43

### **Process Creation (4/4)**

Source: Forte Design Systems

SoC Verification

Prof. Chung-Yang (Ric) Huang

### Other items...

- ◆Port binding (module)

- ◆ Dynamic sensitivity declaration (process)

- **◆**Time resolution

- **◆**Clocks

- Syntax

◆sc\_start()

SoC Verification

Prof. Chung-Yang (Ric) Huang

45

### sc\_start()

- ◆ At the bottom of the sc\_main() function and before the return statement

- Execution of this statement marks the end of elaboration and the start of simulation

- ◆Have an optional argument: sc\_start(arg)

- Specifies the number of time units to simulate (default = forever)

Source: Forte Design Systems

SoC Verification

Prof. Chung-Yang (Ric) Huang

### **Online SystemC Trainings**

- 1. <a href="http://www.forteds.com/systemc/training/index.asp">http://www.forteds.com/systemc/training/index.asp</a> (Free with registration)

- 2. <a href="http://www.doulos.com/knowhow/systemc/tutorial/">http://www.doulos.com/knowhow/systemc/tutorial/</a> (Free)

### Official SystemC website

Open SystemC Initiative (OSCI) http://www.systemc.org

SoC Verification

Prof. Chung-Yang (Ric) Huang

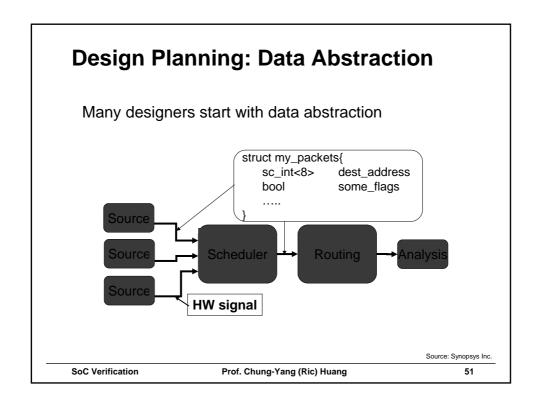

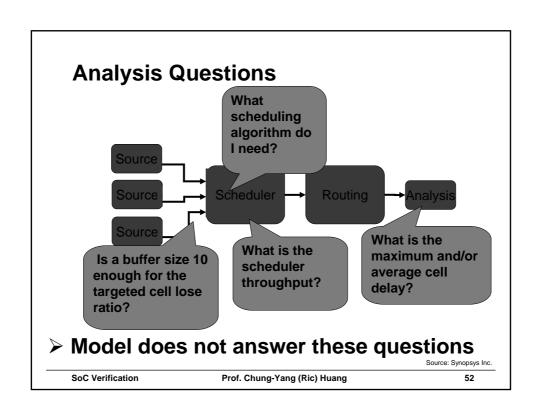

### The Mistakes

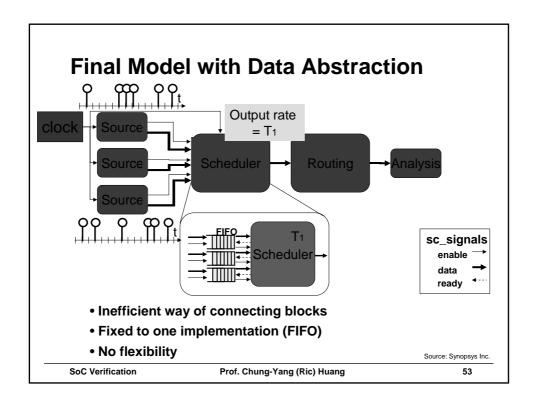

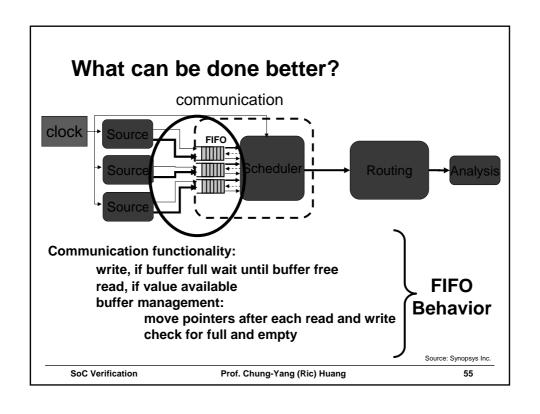

- Mistake 1: Data abstraction does not solve the problem

- Model does not allow to answer the specification questions

- Mistake 2: Using HW signals as communication mechanism

- HW signals are specific for reactive HW

- Signal communication mechanism not suitable for high level models

Source: Synopsys Inc.

SoC Verification

Prof. Chung-Yang (Ric) Huang

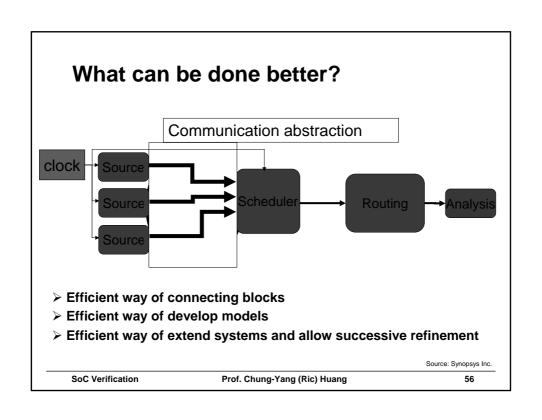

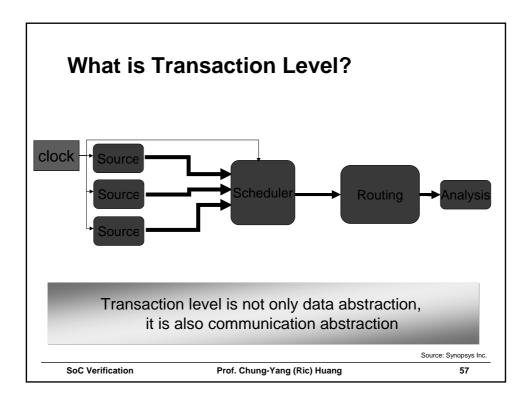

### In short, TLM ---

- ◆ Data + communication abstraction

- Describe how data is communicated between modules

- Can be used to simulate and analyze the system behavior

- ♦ No RTL implementation details

- Greater simulation speed

- Shorter development (modeling) time

- Easier for system analysis and debug

SoC Verification

Prof. Chung-Yang (Ric) Huang

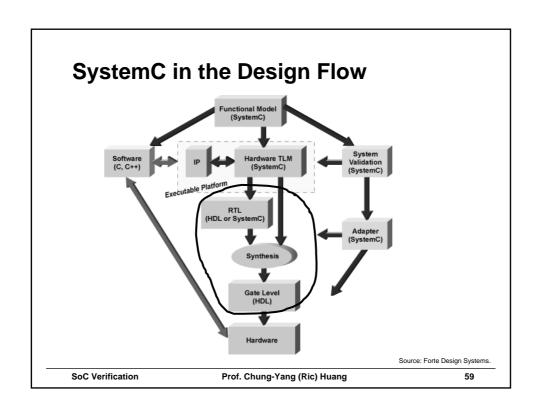

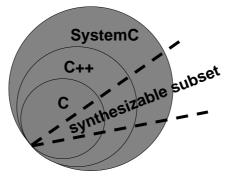

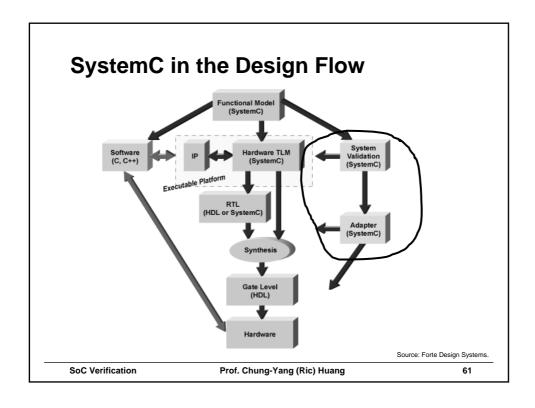

### SystemC Synthesizable Subset

◆A subset of SystemC constructs that can be unambiguously translated into RTL or gate HDL

SoC Verification

Prof. Chung-Yang (Ric) Huang

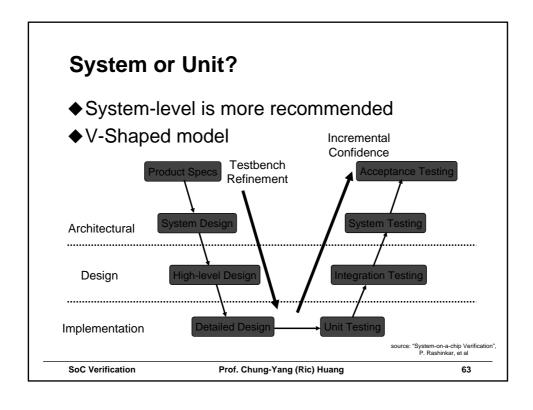

### **System-Level Verification**

- With current available technologies and tools out there, simulation (testbench) approach seems to be the only viable solution

- Testbench creation strategies: 2 options

- System-level testbench first

- Pro: system-level is verified first; problem can be found earlier

- Con: takes more planning and forethought; needs to migrate testbench to lower level(s)

- Unit-level testbench first

- Pro: Familiar to designers; testbench can be created quickly

- Con: Duplicated efforts; system is not well tested

SoC Verification

Prof. Chung-Yang (Ric) Huang

### SystemC Verification (SCV) Library

- ◆SCV 1.0 is now ready for download

- ◆A collection of classes that supports various verification in SystemC

- Data introspection

- Transaction recording

- Constrained randomization

- Utility data types

SoC Verification

Prof. Chung-Yang (Ric) Huang

### **Data Introspection**

- Allows arbitrary data types to provide information about themselves and to manipulate their contents

- Provides a "wrapper" class implementation for normal C++ and SystemC types. The wrapper type acts like a pointer, but has extra introspection methods

- e.g. scv\_smart\_ptr smart\_int;

- Things you can do to svc\_smart\_ptr

- What type are you?

- What is your value?

- Set the value directly.

- Set the value through randomization.

- · Register callbacks.

- When data changes.

- When accessed.

- When written

Source: Forte Design Systems

SoC Verification

Prof. Chung-Yang (Ric) Huang

65

### **SCV Testbench Generation Options**

- ◆ Directed Tests

- Traditional method for testbenches

- ♦ Weighted Randomization

- Focuses stimulus on interesting cases

- ◆Constrained Randomization

- Enables complex and thorough tests to be developed quickly

- ◆Combinations of the above

Source: Forte Design Systems

SoC Verification

Prof. Chung-Yang (Ric) Huang

### **Constrained Randomization**

- Each scv\_smart\_ptr may have its value randomized

- Methods provided to randomize, control, and constrain the randomization and set the seed

- ◆ Example methods:

- next(): generates a uniformly distributed random value

- keep\_out(low\_val, high\_val): tells the random generator to not generate values between low\_val and high\_val.

- keep\_only(low\_val, high\_val): tells the random generator to generate only values between low\_val and high\_val

**SoC Verification**

Prof. Chung-Yang (Ric) Huang

67

### **Utility Data Types**

- ◆ To facilitate stimulus generation

- e.g. The scv\_bag type allows you to create an object where you control the distribution of values by placing objects in the bag

- The relative proportion of objects in the bag determines the weights of distribution

- scv\_bag command\_dist; // a bag of type command command\_dist.add(ADD, 50); // 50% ADD command\_dist.add(SUB, 30); // 30% SUB command\_dist.add(MULT, 10); // 10% MULT command\_dist.add(DIV, 10); // 10% DIV

SoC Verification

Prof. Chung-Yang (Ric) Huang

### **EDA Tools for System-Level (5)**

- ◆Mentor Graphics Seamless CVE

- HW/SW co-verification

- Verifies HW and SW interactions in a virtual prototype

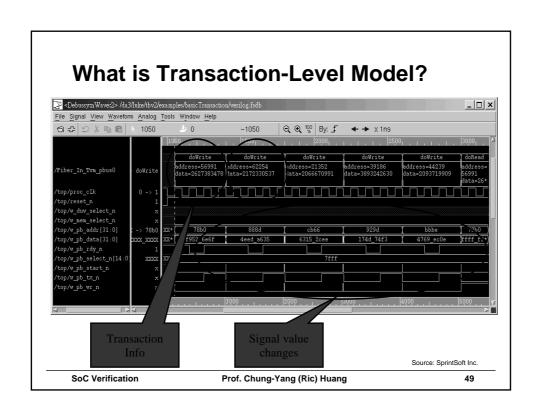

- ◆SpringSoft Verdi + Debussy

SoC Verification

Prof. Chung-Yang (Ric) Huang