# Agenda

## Introduction: SystemVerilog Motivation

Vassilios Gerousis, Infineon Technologies Accellera Technical Committee Chair

## Session 1: SystemVerilog for Design

### **Language Tutorial**

Johny Srouji, Intel

### **User Experience**

Matt Maidment, Intel

## Session 2: SystemVerilog for Verification

### **Language Tutorial**

Tom Fitzpatrick, Synopsys

### **User Experience**

Faisal Haque, Verification Central

Lunch: 12:15 - 1:00pm

### **Session 3: SystemVerilog Assertions**

### **Language Tutorial**

Bassam Tabbara, Novas Software

### **Techhology and User Experience**

Alon Flaisher, Intel

## Using SystemVerilog Assertions and Testbench Together

Jon Michelson, Verification Central

## **Session 4: SystemVerilog APIs**

Doug Warmke, Model Technology

### **Session 5: SystemVerilog Momentum**

## Verilog2001 to SystemVerilog

Stuart Sutherland, Sutherland HDL

### **SystemVerilog Industry Support**

Vassilios Gerousis, Infineon

End: 5:00pm

## SystemVerilog Assertions Language Overview

Dr. Bassam Tabbara Technical Manager, R&D Novas Software, Inc.

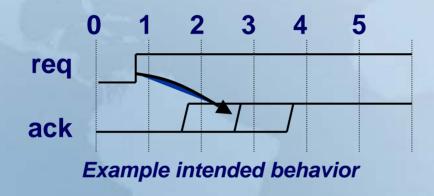

## What is an Assertion?

A concise description of [un]desired behavior

"After the request signal is asserted, the acknowledge signal must come 1 to 3 cycles later"

## SystemVerilog and Assertions

- Enhance SystemVerilog to support Assertion-Based Verification

- White-box (inside block) assertions

- Black-box (at interface boundaries) assertions

- Syntactic compatibility

- Easy to code directly in-line with RTL

- Support for design and assertion reuse

- Support for assertion "binding" to design from separate file

- Monitoring the design

- Concurrent ("standalone") assertions

- Procedural ("embedded") assertions

# System Verilog Assertion Goals

- Expressiveness

- Cover large set of design properties:

- Block Implementation

- Block Interaction

- Usability:

- Easy to understand and use by:

- Design Engineer

- Verification Engineer

- Formalism:

- Formal semantics to ensure correct analysis

- Consistent semantics between simulation and formal design validation approaches

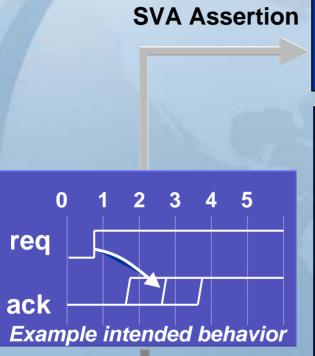

# Concise and Expressive SVA

**HDL** Assertion

```

property req_ack;

@(posedge clk) req ##[1:3] $rose(ack);

endproperty

as_req_ack: assert property (req_ack);

```

```

always @(posedge req)

begin

repeat (1) @(posedge clk);

fork: pos pos

begin

@(posedge ack)

$display("Assertion Success",$time);

disable pos pos;

end

begin

repeat (2) @(posedge clk);

$display("Assertion Failure",$time);

disable pos pos;

end

join

end // always

```

The Basics

4 Easy Lessons

## **Immediate assertions**

```

assert ( expression ) action_block;

action_block ::= [statement] [else statement]

```

- Appears as a procedural statement

- Follows simulations semantics, like an "if"

if (expression) action\_block;

- Action block

- Executes immediately

- Can contain system tasks to control severity, for example: \$error, \$warning, ...

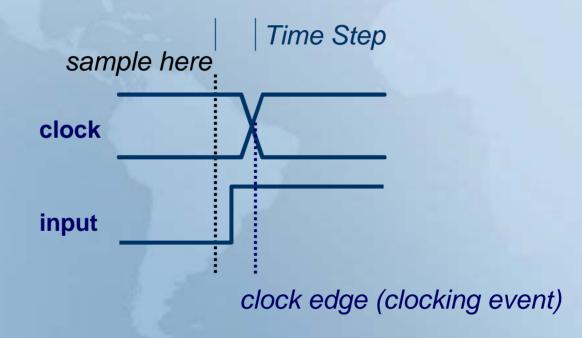

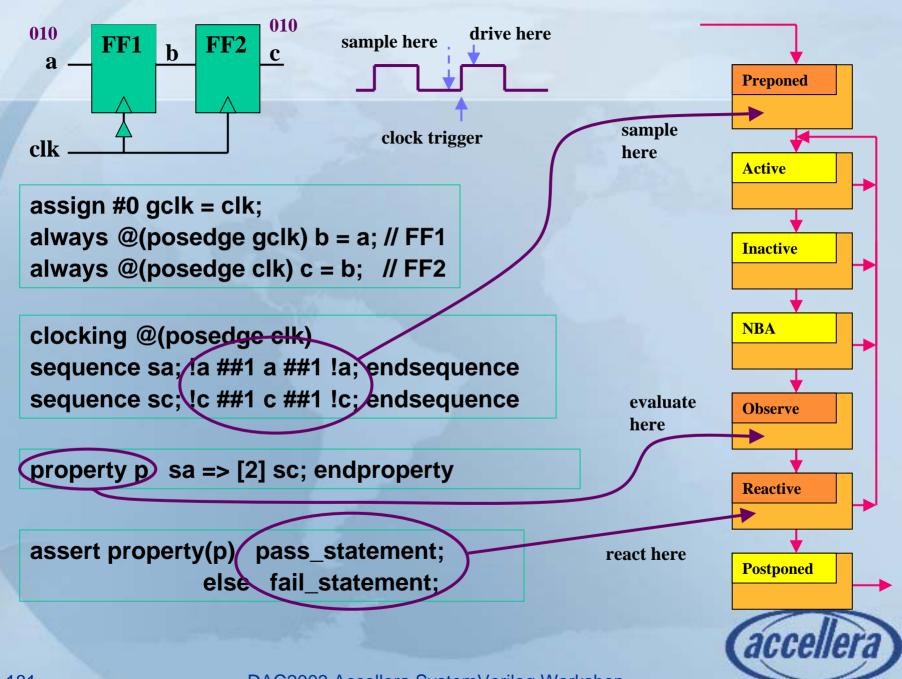

## Concurrent assertions

```

assert property ( property_instance_or_spec )

action_block;

action_block ::= [statement] [else statement]

```

- Appears outside/inside procedural context

- Follows cycle semantics using sampled values

- Action block

- Executes in reactive region

- Can contain system tasks to control severity, for example: \$error, \$warning, ...

# **Assertion Sampling**

Values sampled at end of previous Time Step

# Hierarchy of Assertion Constructs

Assertion Directives

Property Declarations

Sequential Regular Expressions

Boolean Expressions

assert, cover, bind, declarative instantiation, procedural instantiation

disable iff, not,

implication

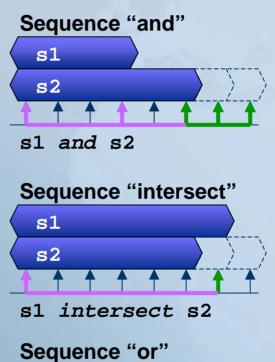

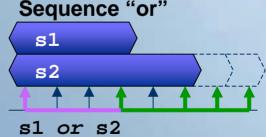

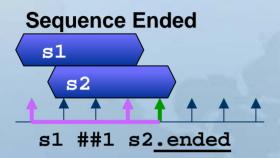

repetition,(cycle)delay,

and, or, intersect,

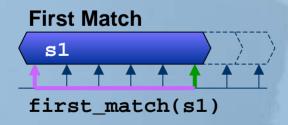

first\_match,

within, throughout

<expr>, <function>,

<temporal\_edge\_function>,

ended, matched

## Congratulations !!!

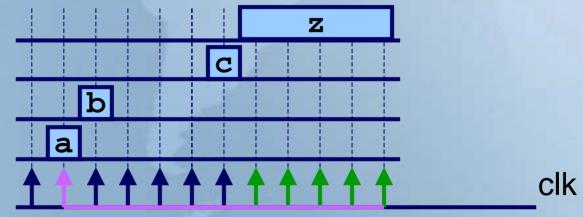

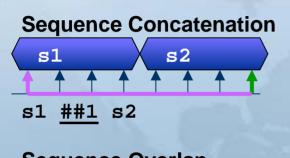

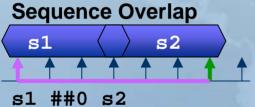

# Sequential Regular Expressions

- Describing a sequence of events

- Sequences of Boolean expressions can be described with a specified time step in-between

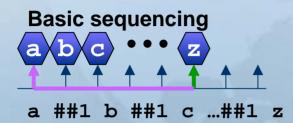

@(posedge clk) a ##1 b ##4 c ##[1:5] z;

# Regular Expression Examples

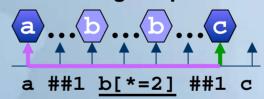

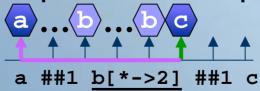

#### **Sequence with Delay**

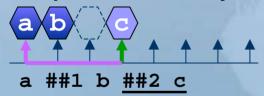

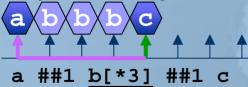

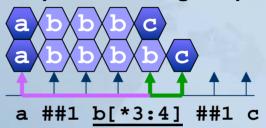

## **Expression Repetition**

#### **Expression Range Repetition**

## **Expression Non-Consecutive** "Counting" Repetition

#### **Expression "Goto" Repetition**

## Sequences Encapsulate Behavior

Can be Declared

```

sequence <name>[(<args>)];

[@(<clocking>)] <sequence>;

endsequence

sequence s1(a,b);

@(posedge clk) a[*2] ##3 b;

endsequence

```

Sequences Can Be Built From Other Sequences

```

sequence s2; @(posedge clk) c ##1 d;

endsequence

sequence s3; @(posedge clk) s1(e,f) ##1 s2;

endsequence

```

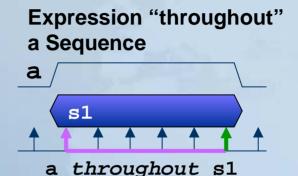

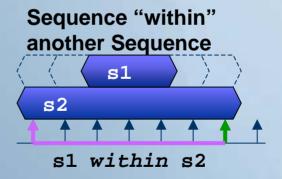

- Operations to compose sequences

- and, or, intersect, within, throughout

# **Sequence Operations**

# More Sequence Operations

DAC2003 Accellera SystemVerilog Workshop

#### **Temporal Edge Functions**

# **Property Definition**

- Property Declaration: property

- Declares property by name

- Formal parameters to enable property reuse

- Top Level Operators

```

not desired/undesired

disable iff reset

```

- | -> , | => *precondition*

- Assertion Directives

- assert checks that the property is never violated

- cover tracks all occurrences of property

## **Property implication**

```

sequence_expr |-> [not] sequence_expr

sequence_expr |-> [not] sequence_expr

```

- |-> is overlapping implication

- |=> is non-overlapping implication same as:

```

sequence_expr ##1 `true | -> [not] sequence_expr

```

Most commonly used to attach a precondition to sequence evaluation

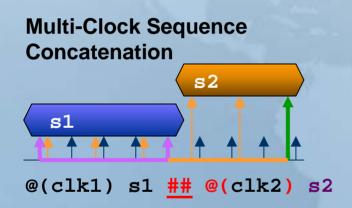

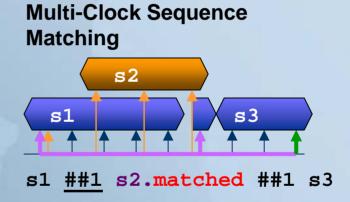

## Multiple Clock Support

Clocking event controls must be specified for each subsequence

# **Manipulating Data: Local Dynamic Variables**

- Declared Locally within Sequence/Property

- New copy of variable for each sequence invocation

- Assigned anywhere in the sequence

- Value of assigned variable remains stable until reassigned in a sequence

**Local Dynamic Variable Example**

```

valid

in

EA

BF

out

EB

property e;

int x;

(valid,(x=in))| => ##5(out==(x+1));

endproperty

```

# **Embedding Concurrent Assertions**

```

sequence s1;

(req && !gnt)[*0:5] ##1 gnt && req ##1 !req;

endsequence

Automatically Updates

always @(posedge clk or negedge reset)

Enabling Condition as

if(reset == 0) do_reset;

Design Changes

else if (mode == 1)

Infers clock from

case(st)

instantiation

REQ: if (!arb)

if (foo)

Requires User to Update

st <= REQ2:

Manually as Design

PA: assert property (s1);

Changes

property p1;

@(posedge clk) ((reset == 1) && (mode == 1)

&& (st == REQ) && (!arb) && (foo)) => s1;

endproperty

DA: assert property (p1);

```

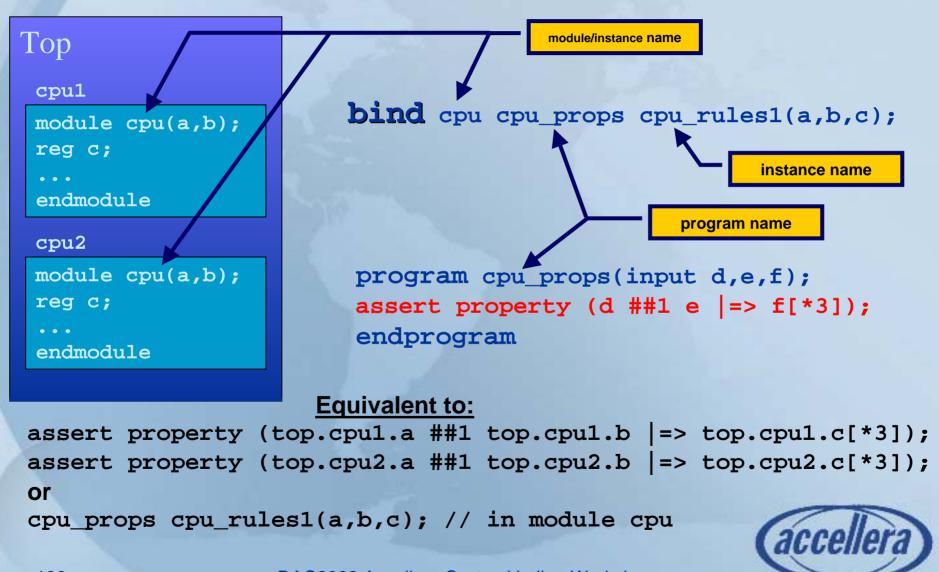

## **Bind statement**

bind module\_or\_instance\_name instantiation;

- No semantic changes to assertion

- Minimal change to design code

- Assertions included in the instantiation

- Allows binding a module, program and interface instance

- Mechanism to attach verification IP to module or module instance

## **Bind statement**

bind module\_or\_instance\_name instantiation;

# SystemVerilog Assertions Summary

- Use clocked/sampled semantics for signals

- Ensure compatibility with formal & synthesis tools

- Avoid race conditions

- Declarative assertions add flexibility

- Monitoring and evaluation

- Reuse

- Support design/assertion IP creation and reuse

- Enhanced scheduling allows building reactive testbenches

- Enhanced coverage of functional spec