本實驗室的研究領域包括了低功率、高速、高解析度的“類比/數位轉換器”與“數位/類比轉換器”應用於有線/無線通訊,類比前端電路應用於60GHz收發機及寬頻高速的高階量測儀器系統,電源能量擷取系統,高速I/O電路應用於SDRAM DDR4,低抖動鎖相迴路/延遲鎖定迴路時脈產生應用於混合信號系統和類比/混合信號積體電路設計實作應用於系統晶片。類比/數位轉換器的架構包括了循序漸近式(SAR)、管線(pipeline)、子區間(subranging)、快閃(flash) 和時間交錯(time-interleave)。數位/類比轉換器的研究將專注於電流切換區段(current-steering segmented)架構。就能量擷取電源轉換器的研究而言,要達成高效率和低暫態突波。就低抖動鎖相迴路/延遲迴路的研究而言,將強調其使用來避免時脈誤差(clock skew)在高速高精確度的類比/數位轉換器系統。就高速I/O電路的研究而言,結合信號與電源完整度的考量,將達成高速、低電源電壓的目標。總的來說,研究專注於低功率、高速混合信號積體電路設計。

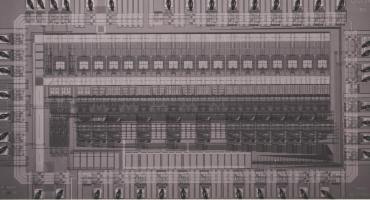

14-bit 20 MS/s Pipelined ADC in 0.5-μm CMOS (4.5×2.4 mm2) |

|

© 國立台灣大學電子所混合訊號實驗室 |